- 全部

- 默认排序

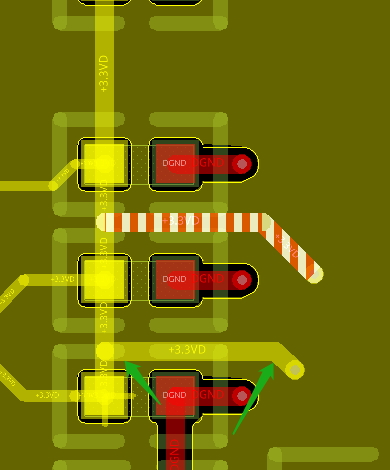

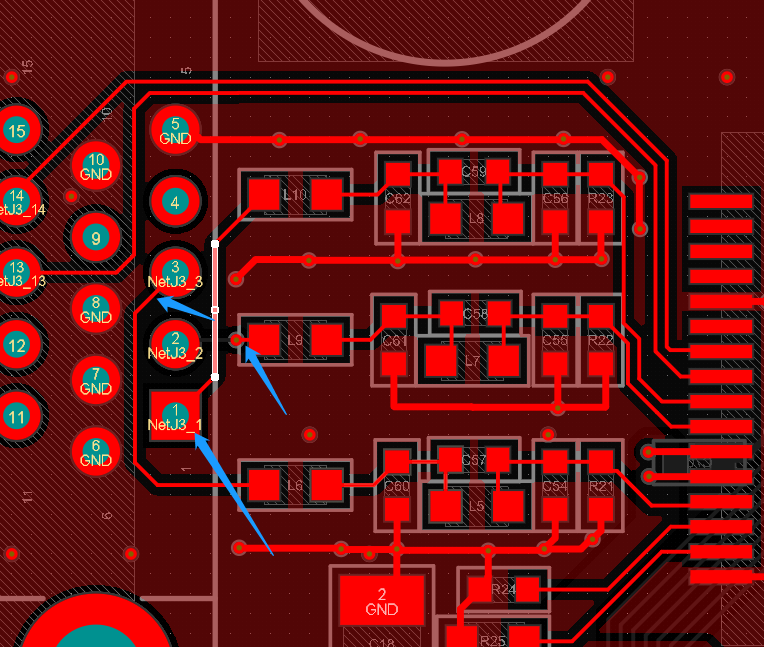

注意此处扇孔可以直接打在走线中间,这样拉出去形成了直角:注意个别过孔的间距,不要割裂了铜皮:注意数据组跟地址控制时钟组之间用GND走线隔开:再有空间的情况下 ,自己处理下。等长注意GAP尽量大于等于3W长度:优化处理下。其他的等长误差没什么

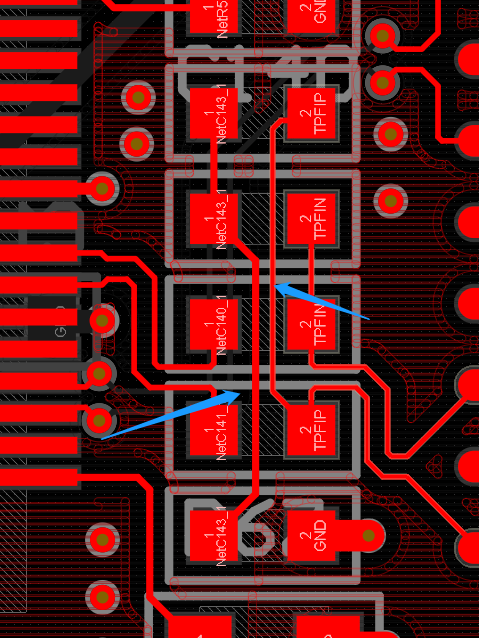

走线不要从电阻电容中间穿,后期容易造成短路,可以打孔走底层2.跨接器件旁边尽量多打地过孔3.数据线和地址线等长都需要满足3W4.电感下面尽量不要走线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

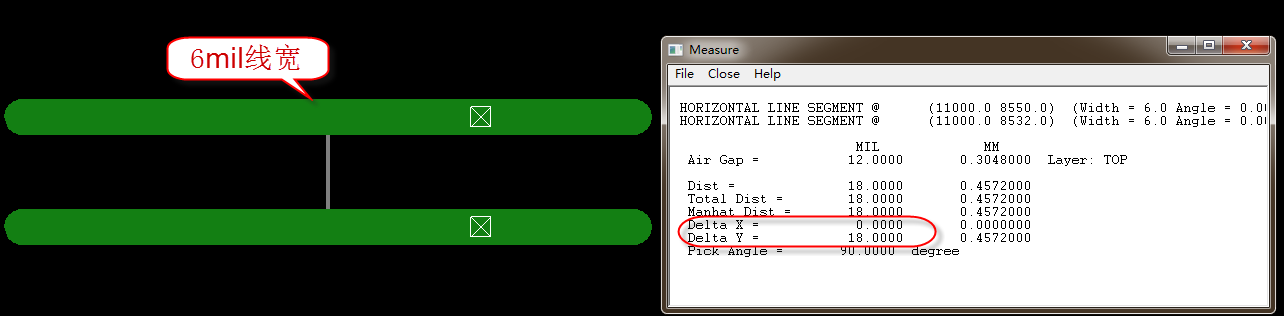

USB走线控制90R,走线宽度6mil,中心间距12mil,这是我目前用的,这样是不是不符合3W了? 是不是要重新用SI9000计算一个符合90R同时符合3W的线宽和间距呢?

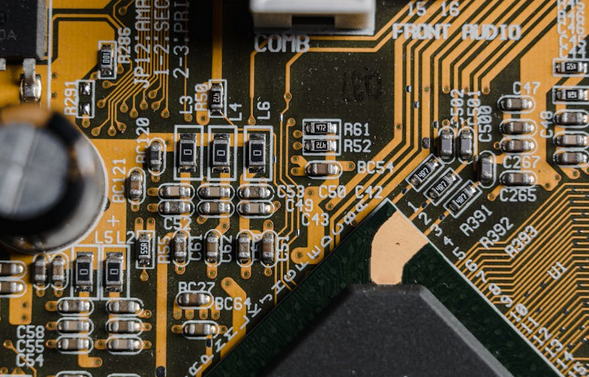

在电子设计中,印刷电路板(PCB)设计是至关重要的一环,它涉及多方面的考量,包括电器性能、热性能、机械强度等,为了确保电路的稳定性及可靠性,3W原则、20H原则及五五规则是必不可少的,下面将谈谈这些规则。1、3W原则:功率与散热的权衡3W原

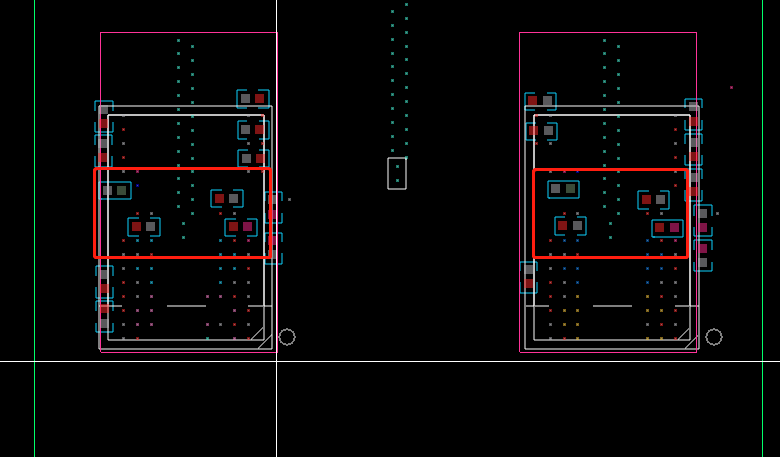

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在Allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

确认一下此处是否满足载流,自己加宽一下铜皮2.注意等长线需要满足3W规则3.注意器件摆放不要干涉1脚标识以上评审报告来源于凡亿教育邮件公益作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.c

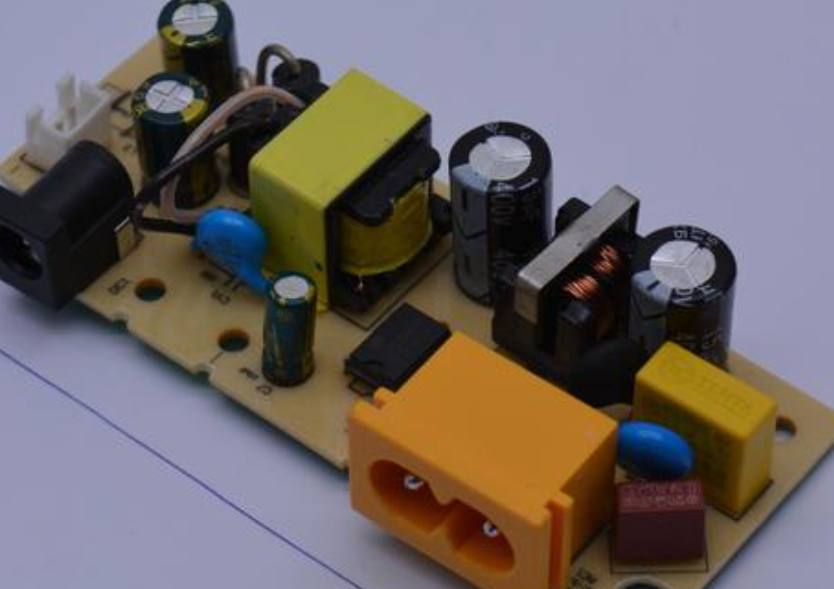

DC/DC电源指直流变换为直流的电源,从这个定义看,LDO也应归属于DC/DC电源,但一般只将直流变换到直流,且这种转换是由开关方式而实现的电源称为DC/DC电源对于LDO的优点是低噪声低纹波、应用简单、成本低、输入/输出几乎无延时,而缺点是功耗大、效率低、只能用做降压变换、只支持小电流的输出(受散热条件的限制,LDO最大功耗不能超过3W)、无法实现输入/输出的隔离。LDO的这种特性与其内部的晶体管(或 MOSFET)工作于线性区有关。DCDC则基本克服了LDO所具有的缺点,DCDC电源的 MO

VGA的模拟信号需要加粗2.数据线等长需要满足3W规则3.地址线也需要满足3W规则4.挖空电感所在层即可5.变压器除差分之外其他的信号都需要加粗20mil6.外壳地和GND的间距最少需要20mil7.网口差分需要进行对等长,误差为5mil8

个别器件注意整体对齐:注意等长线之间需要满足3W间距原则:没满足的都自己优化下。数据线组内也需要满足3W:差分对内等长误差为5MIL:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

扫码关注

扫码关注