- 全部

- 默认排序

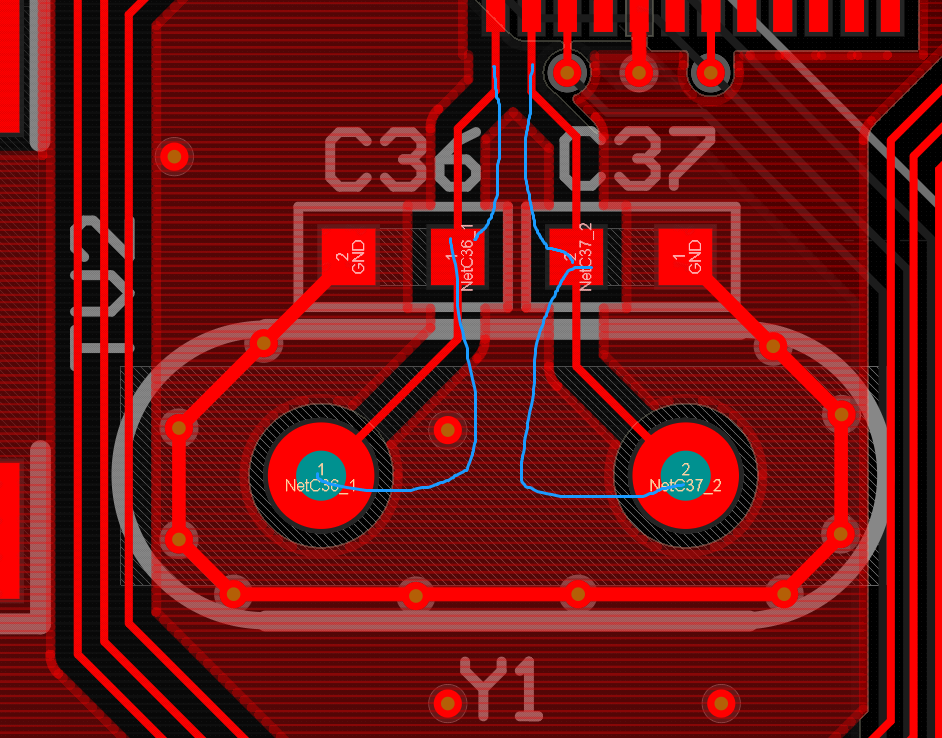

晶振走内差分需要再优化一下2.地分割间距最少1mm,建议2mm,有器件的地方可以不满足3.反馈信号走线需要加粗4.电感中间挖空就不要有铜皮5.输出打孔要打在电容后面6.注意过孔尽量盖油,不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特

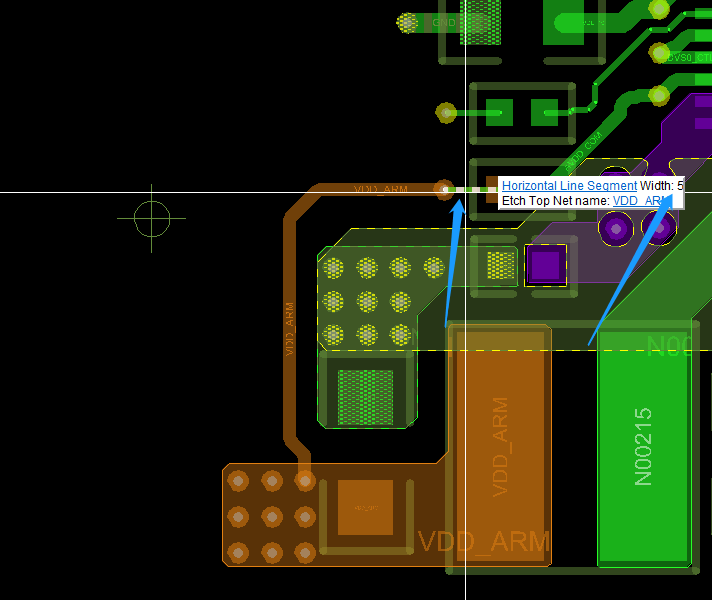

反馈线需要走一根10mil的线,线宽尽量保持一致2.此处是输主干道,两个过孔不满足载流3.存在无网络铜皮和过孔4.此处器件在底层无法与顶层铜皮进行连接5.电源和地存在开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB

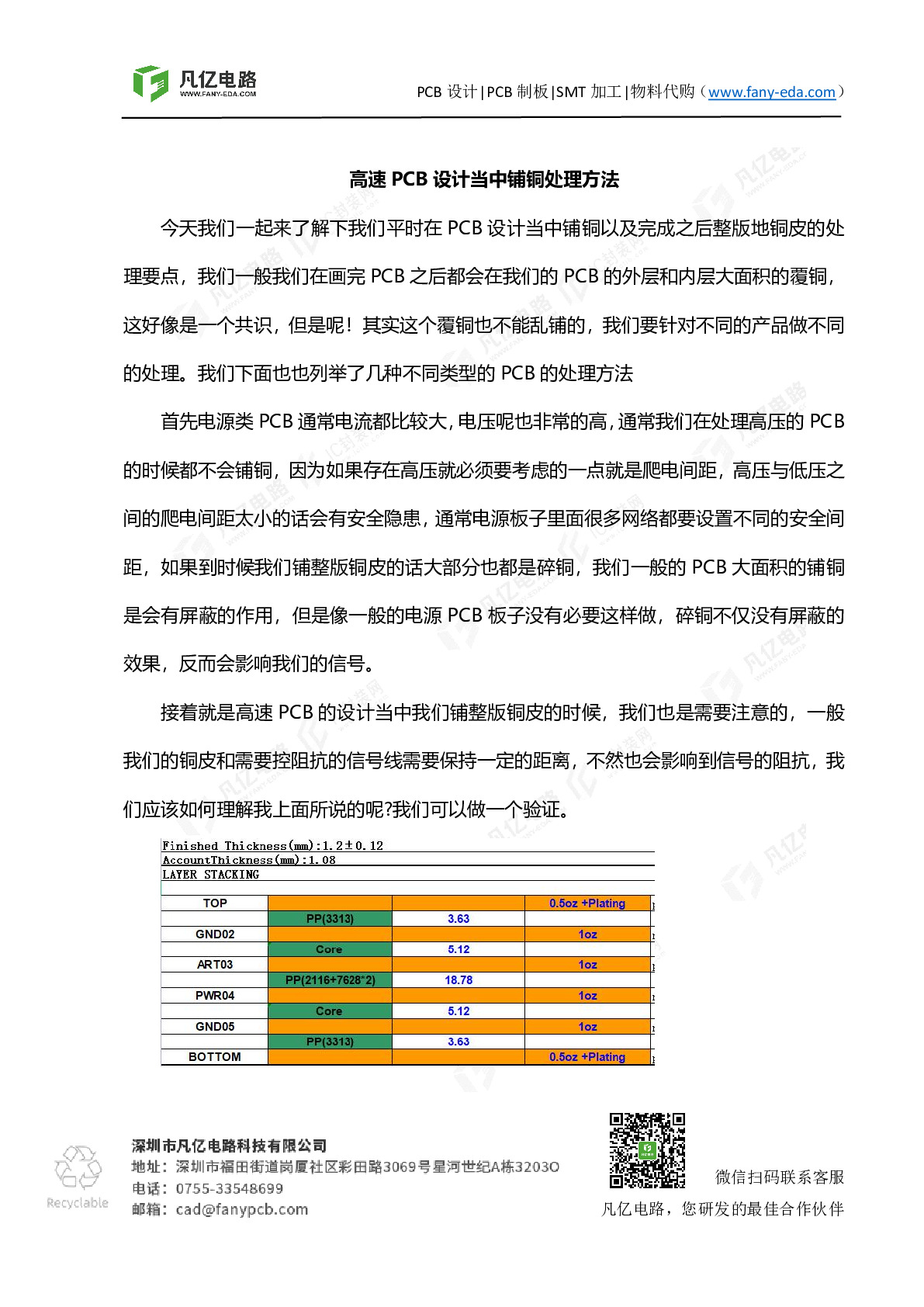

随着电路微型化程度的不断提高,元件和布线技术也取得巨大进步,目前现在的电子元件的布线设计方式直接决定着后续制作流程中的测试能否很好进行,可良好的可测试性能大大减少生产测试的准备时间和费用。下面就聊聊高速PCB设计的可测试性是什么?有什么用?

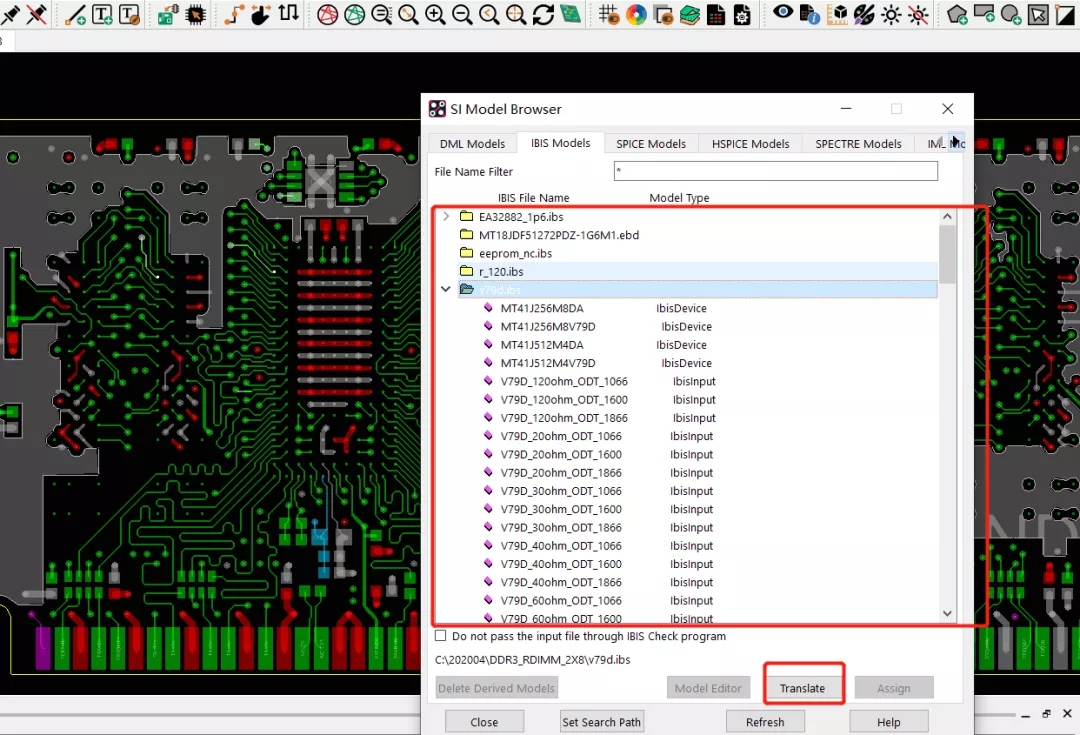

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

要点:1.高速PCB在设计中常见的问题;2.高速PCB的特殊材料要求;3.高速信号传输的特征和挑战4.高速PCB设计的原则和考虑因素5.PCB设计存在问题6.高速信号仿真分析工具有那些7.项目实例,高速PCB的信号完整性仿真办法和技巧

扫码关注

扫码关注