- 全部

- 默认排序

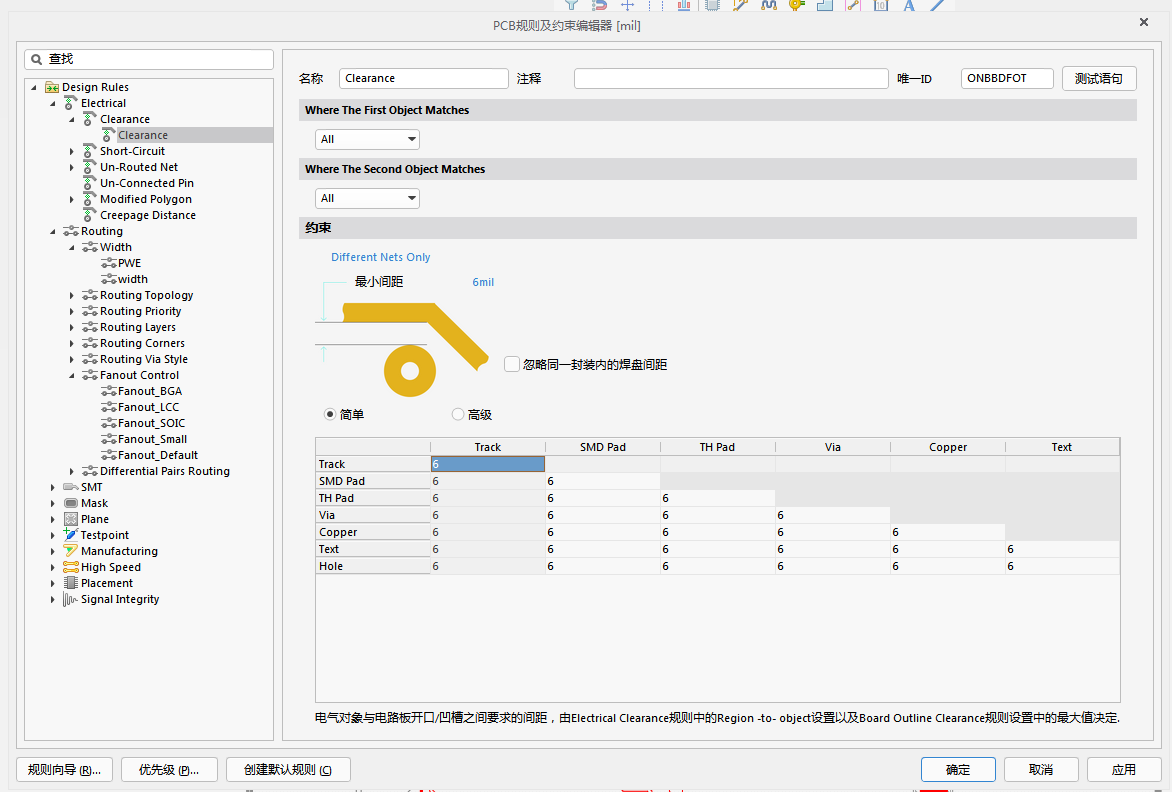

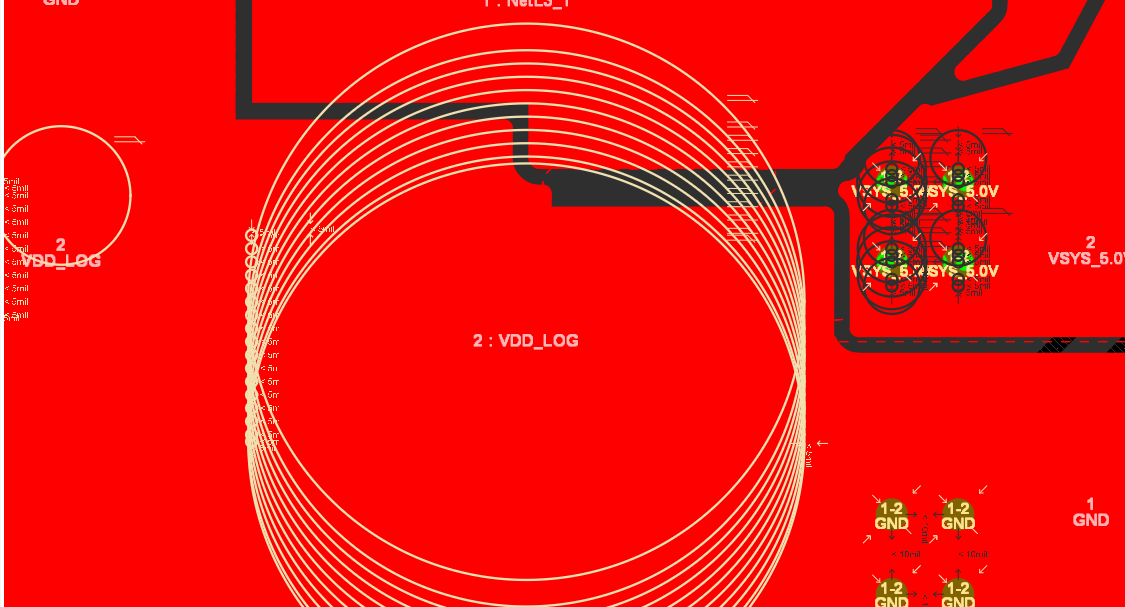

Pcb布线完成后,要查找没有连接上的网络,在整板布线后,可能有些没有连接上的网络打开飞线也显示不出来,去整板找很费时费力 ,且不一定能找出,这里就有 一个快捷的迅速找到所有没有连接网络。

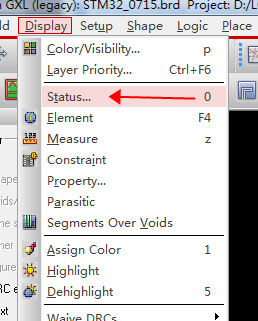

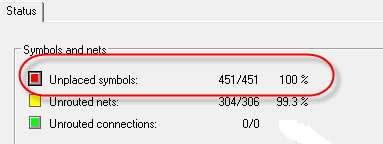

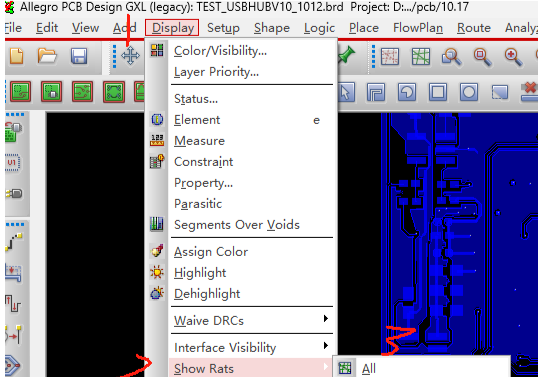

很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:第一步,需要检查原理图的网表是否导入成功,执行菜单命令Display,在下拉菜单中选择Status,整个PCB文件的状态,如图324-1所示,进入到状态的界面,最上面一栏是Symbols and nets的选项,网表导入成功

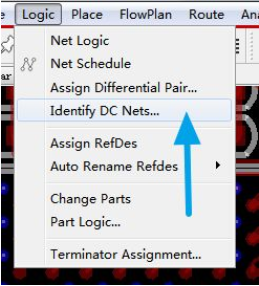

由于规划没设好,导致D5的一端与电容C47悬空,排电路时D5与C47之间没有飞线。其它器件又定位好,不想重新布线网络,有什方法在现有的器件布局下,重新产生飞线网络?

Cadence Allegro飞线的隐藏关闭在PCB设计过程中,一把布线的顺序是先走信号线,然后进行电源的处理、电源的分割,然而电源的飞线是非常多的,非常影响信号线的布线,所以刚开始会将电源的飞线进行隐藏,具体操作的步骤如下所示:1. 点击

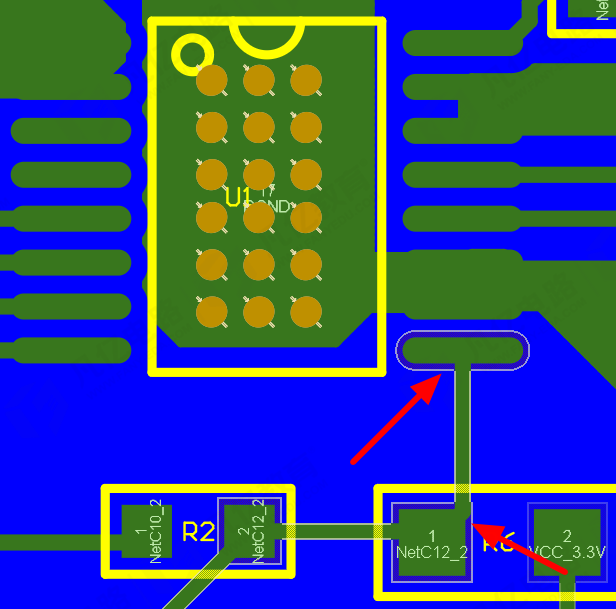

还存在较多短路报错,对应报错区域自己检查下:存在飞线:注意电感内部挖干净一点:注意铜皮不要尖角以及直角,整合下全部都钝角铺铜:走线也不能直角:这种铜皮完全不合格,板上类似铜皮都要重新绘制再去铺铜:走线要么没有从焊盘中心拉线,要么没有完整从焊

很多电子工程师会选择Allegro设计电子电路,其中之一是隐藏/显示飞线操作,但很多小白不会操作,所以今天讲讲Allegro如何隐藏/显示飞线,希望对小伙伴们有所帮助。1、为什么要隐藏/显示飞线?首先我们要理顺各个模块的布局思路,从而规划整

1.焊盘出线应该从焊盘长方向出线,小器件应从焊盘中间出线,避免焊接问题2.地网络铺铜需要加粗和电源一样宽3.两个测试点存在飞线4.相邻大电感应朝不同方向垂直放置5.连接到9号焊盘的走线是反馈信号,不需要加粗以上评审报告来源于凡亿教育90天高

扫码关注

扫码关注