- 全部

- 默认排序

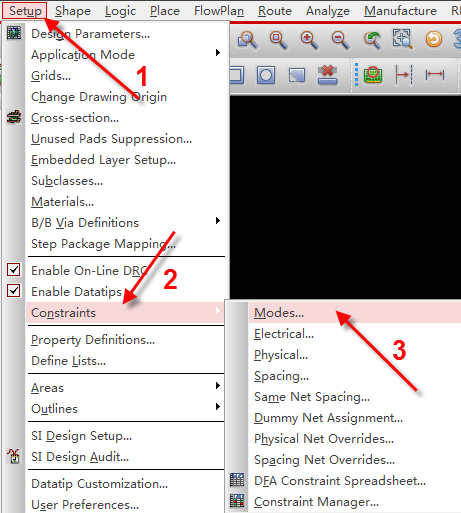

答:我们在前面的问答中讲述了走线的阻抗线宽以及不同的元素之间的间距规则之间的限定,但是,在Allegro软件中各个的约束规则需要在约束规则管理模式开启的情况下,才能起作用的。执行菜单命令Setup-Constrains,在下拉菜单中选择Modes,进行各个约束规则管理模式的选取,如图5-79所示:

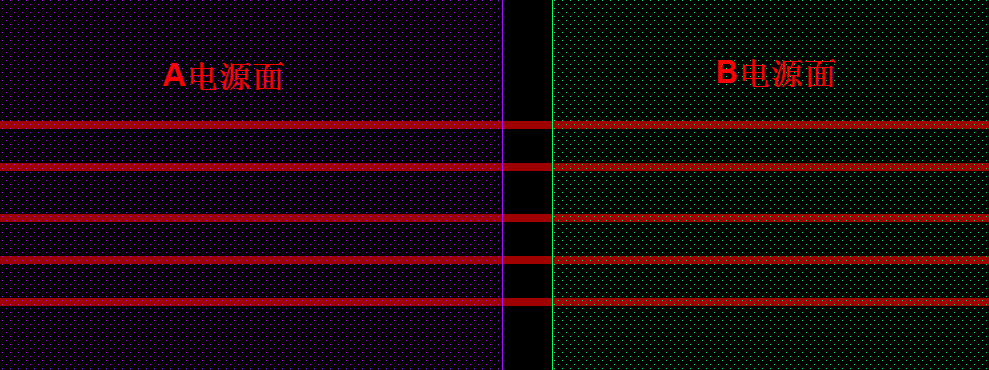

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。

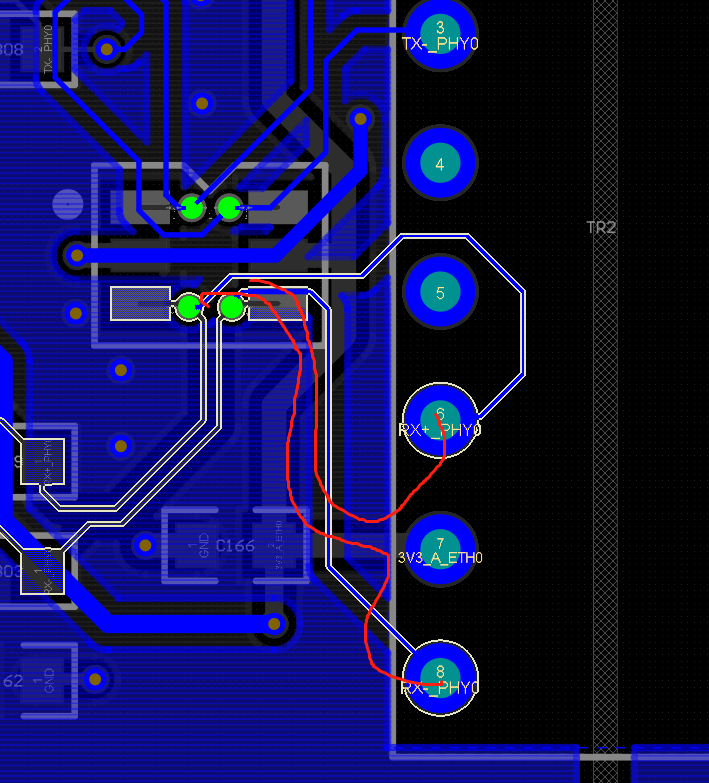

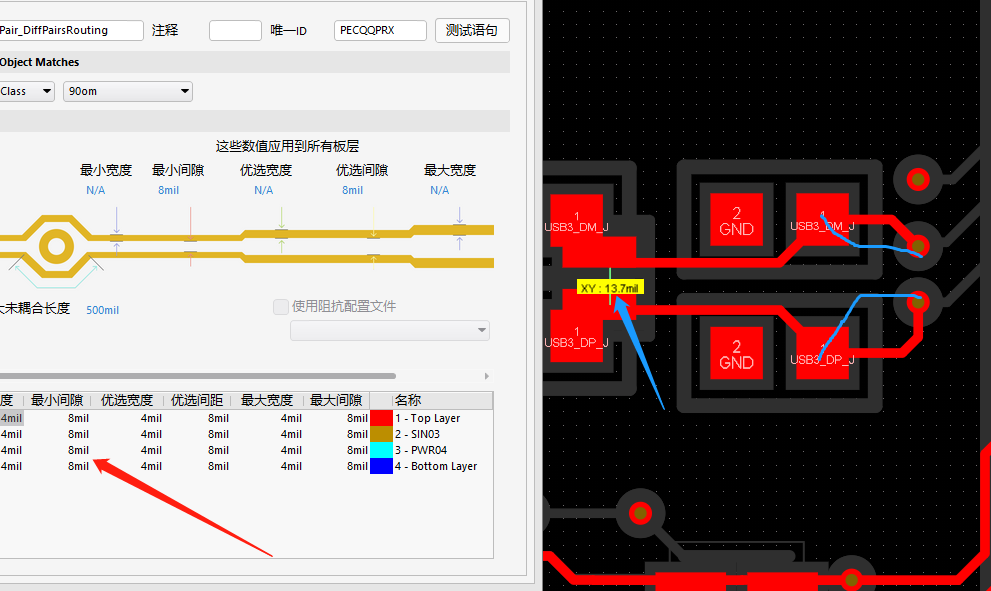

差分线要按阻抗线宽线距要求耦合走线网口到芯片的差分都需要优化,后期自己好好理解差分,然后走线需要调整一下2.器件摆放尽量中心对齐处理3.走线需要优化一下,不要有锐角4.TX分组错误5.注意等长蛇形走线尽量45度,不要直角6.除了散热过孔,其

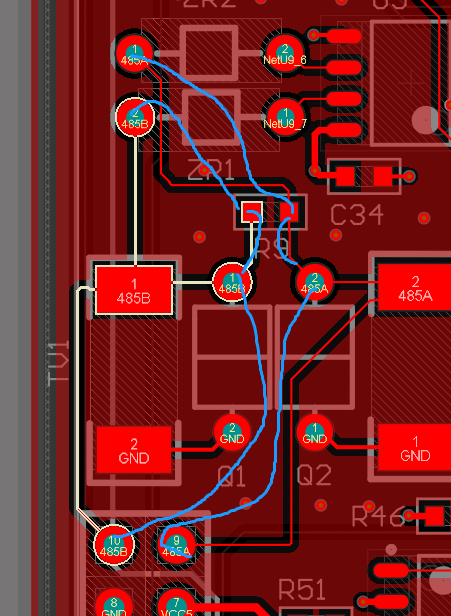

1.485需要走类差分处理或者加粗2.模拟信号需要一字型布局,走线需要加粗,并包地处理3.晶振需要走类差分处理晶振走线都需要优化一下4.差分走线需要按照阻抗线宽线距要求走,后期自己优化一下5.注意地分割,模拟地不要进去数字地里面,分割间距1

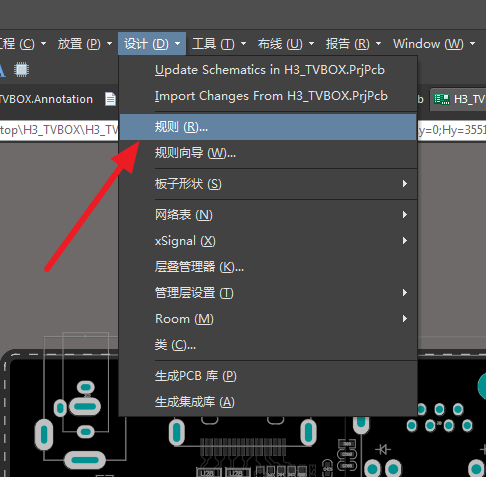

在我们进行PCB设计的时候,布线规则设置也是我们及其重要的一项。布线规则中着重关注的是线宽规则和过孔规则。因为在进行高速PCB设计的时候一般需要用到阻抗线,那么对于每层的线宽要求是不一致的。而且有时候又考虑到电源线的特殊性,对于电源线线宽有特殊的要求。所以我们的线宽规则的重要性不容置疑了。那么我们对于过孔规则就是考虑到在生产的时候不要过多的过孔属性类型,因为种类太多的话,生产的时候就要频繁的换钻头,所以一个PCB设计中不要超过两种过孔类型。

差分走线要按照阻抗间距走,差分出线要尽量耦合,后期自己优化一下有好几处差分没有按照阻抗线距走,后期自己调整一下2.差分对内等长凸起高度不能超过线距的两倍3.CC1和CC2属于重要信号,走线需要加粗4.走线需要优化一下,尽量不要有直角5.差分

前期为了满足各项设计的要求,我们会设置很多约束规则,当一个PCB单板设计完成之后,通常要进行DRC(Design Rule Check)检查。DRC检查就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项电气规则检查。常见的检查项包括间距、开路以及短路的检查,更加严格的还有差分对、阻抗线等检查。

在我们进行PCB设计的时候,布线规则设置也是我们及其重要的一项。布线规则中着重关注的是线宽规则和过孔规则。因为在进行高速PCB设计的时候一般需要用到阻抗线,那么对于每层的线宽要求是不一致的。而且有时候又考虑到电源线的特殊性,对于电源线线宽有特殊的要求。所以我们的线宽规则的重要性不容置疑了。那么我们对于过孔规则就是考虑到在生产的时候不要过多的过孔属性类型,因为种类太多的话,生产的时候就要频繁的换钻头,所以一个PCB设计中不要超过两种过孔类型。等等以上都是我们设置布线规则的重要性。

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。

扫码关注

扫码关注