- 全部

- 默认排序

差分走线等长调节

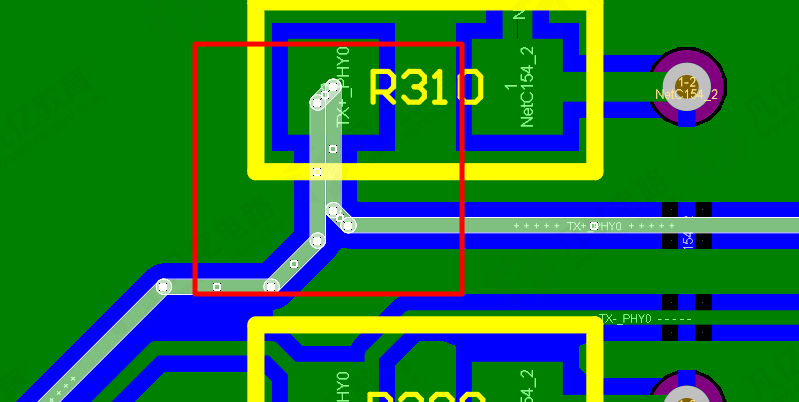

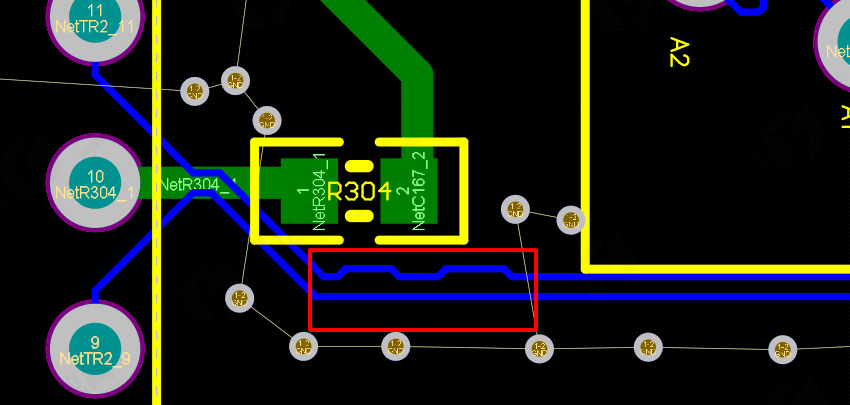

最近在画板子很多USB接口,都是差分线,差分线会走,在AD里面快捷键P+I就可以走差分线了,但是差分线两端直接走线过去的长度可能需要绕一下才能达到另一端。问题1:如果一对差分线,其中一条需要绕一下才能和另一条等长,那么怎么只绕其中一条,而另一条不饶呢?问题2:以前的差分线都是直接走常规线,一条一条的

在PCB布局布线时,很多新人工程师可能会听见这种说法,类似于“PCB蛇形线越多,就显得板子高级”,虽然蛇形线可以调整长度,满足特定的时序要求,平衡线路间的长度差异,但这种说法在大多数情况下是错误的!1、尽量减少蛇形线的使用蛇形线虽然能解决部

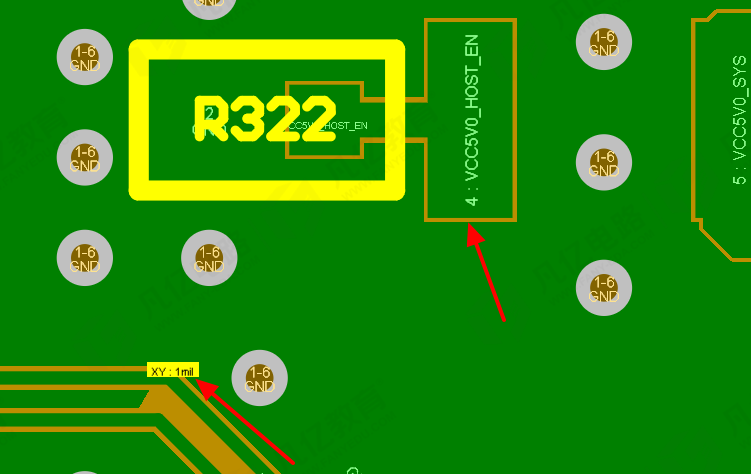

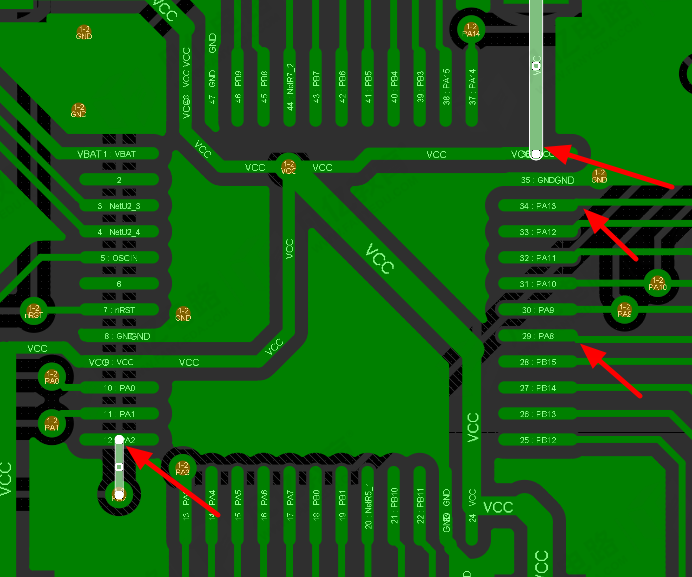

铜皮间距太小,所有间距最小不能小于4mil多处孤岛铜皮、尖细铜皮差分出焊盘尽快耦合优化布局走线尽量靠近,不会可以查看参考板走线太细,走线一般情况最细4mil,明明可以走4mil线宽差分对内等长绕线在引起不等长处绕线差分对内等长绕线拱起处长度

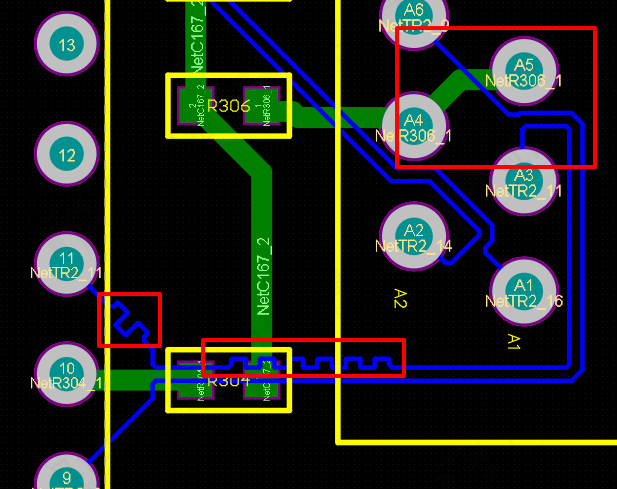

差分连接焊盘走线不要重叠、锐角,两边保持一致变压器除差分走线以外其他所有走线加粗到20mil以上差分走线尽量耦合差分走线出焊盘尽快耦合保持长度一致时钟信号包地打孔处理rx、tx分别建立等长组控制100mil误差分别等长走线应连接到焊盘中心,

差分对内等长错误,应在引起不等长端绕线,绕线长度走线避免锐角同层链接多余打孔焊盘不完全连接,应连接到焊盘中间焊盘出线应避免从四角出线、在焊盘内拐弯以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

差分对内等长错误,按照等长绕线高度和长度不符合规范焊盘没有开窗相邻器件尽量朝相同方向整齐放置走线避免锐角对内等长误差不达要求,差分对内等长误差要求在5mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

焊盘从短方向出线,不要从长方向和四角出线,从焊盘中心出焊盘后拐弯主电源输出打孔要在模块最后一个电容后方,多打孔加大载流 SD走线保持3w间距整组打孔包地usb差分对经过电阻后而然是差分对,按照差分布线尽量耦合减短换层走线长度,换层打孔旁边打

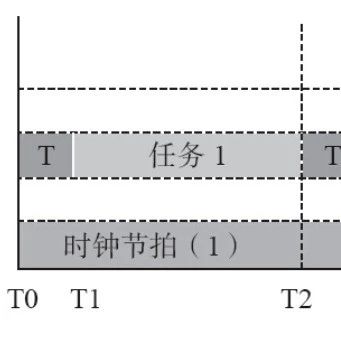

任务A和任务B按照等长时间轮流占用处理器,在单处理器上造成多个任务同时运行的假象。这里先聊一聊多任务系统架构的分割时间段。将处理器运行时间分成小的时间段指明了把处理器时间以多大的频率分割成固定长度的时间片段,也叫做多任务系统架构的时钟节拍。作为多任务系统运行的时间尺度,时钟节拍是通过特定的硬件定时器

单对差分对包地50-100mil打孔差分信号走线换层在旁边打回流地过孔同层连接多余打孔多处飞线未连接差分对内长度误差5mil,设置对内等长规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

扫码关注

扫码关注