- 全部

- 默认排序

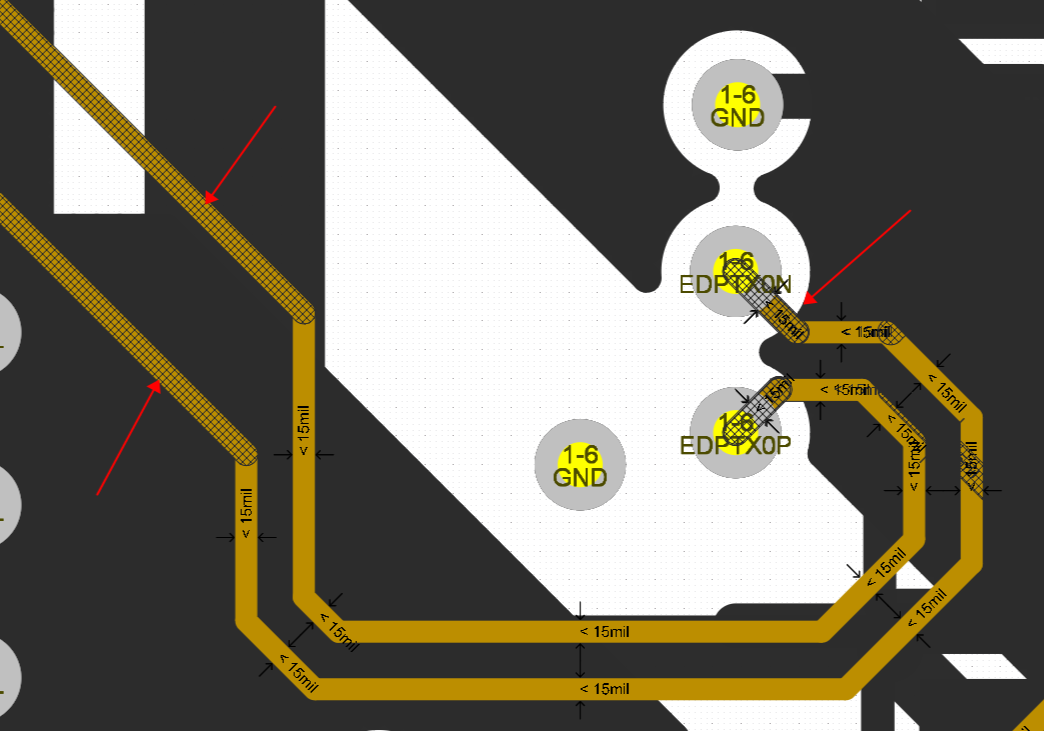

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

在数字创新主导的时代,深度伪造视频的兴起已成为普遍关注的问题。深度伪造(深度伪造s)是一种人工智能生成的视频,可以将图像操纵并叠加到现有的镜头上,其有可能以前所未有的规模欺骗和操纵观众。随着技术的进步,需要强大的解决方案来应对日益严重的错误

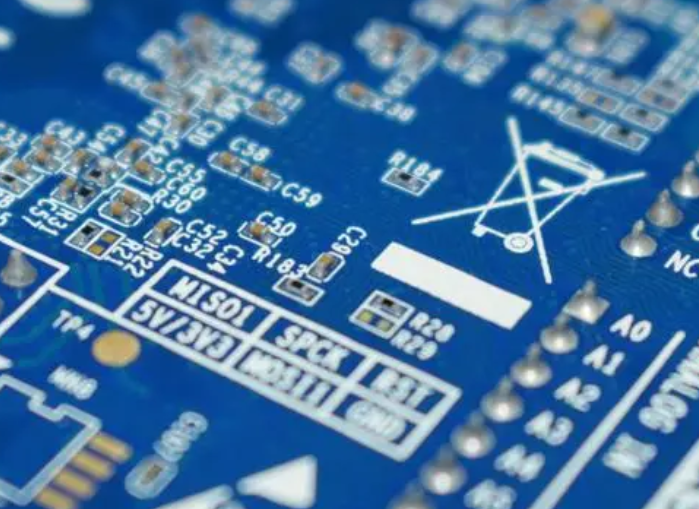

PCB Layout是一款功能强大的PCB设计软件,相比其他EDA软件,Pads Layout偏重于PCB布局,因此被广泛应用在各种电子产品的开发中,在使用Pads Layout时,有些技巧可帮助提高提高设计效率和减少错误,下面来看看有哪些

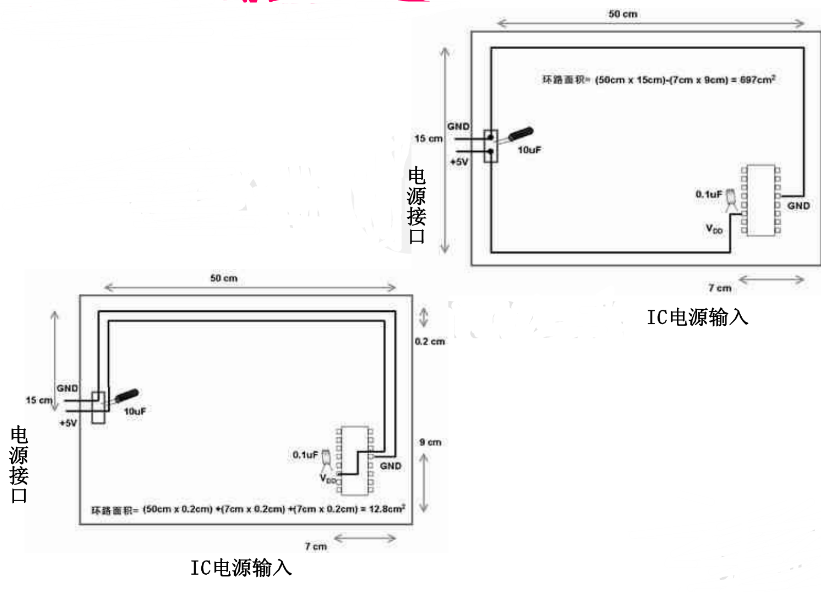

PCB Layout是高速PCB设计的重要部分,一直以来是电子工程师需要花很多精力的存在,而且一旦设计错误将推倒重来,不仅费力费时,还拖慢进度,那么有没有可以加快PCB Layout设计的方法?1、为确保正确实现电路,应遵循的设计准则尽量采

对于电子工程师来说,理解并计算PCB的阻抗和损耗是非常重要的,若是计算错误,很有可能导致电路板无法以最佳效率运行,那么针对这两个参数,该如何计算?首先,要想计算PCB的阻抗和损耗,必须先了解电感和电阻的基本概念:①电感(L):电感是衡量线圈

在PCB布局布线时,很多新人工程师可能会听见这种说法,类似于“PCB蛇形线越多,就显得板子高级”,虽然蛇形线可以调整长度,满足特定的时序要求,平衡线路间的长度差异,但这种说法在大多数情况下是错误的!1、尽量减少蛇形线的使用蛇形线虽然能解决部

扫码关注

扫码关注