- 全部

- 默认排序

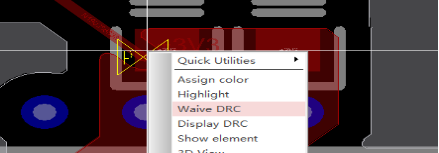

答:对于PCB上某些DRC,是可以忽略,可以通过Waive DRC将此DRC隐藏。第一步,在Find选项卡中勾选DRC errors;第二步,然后将光标移动到DRC附近,右击选择Waive DRC,如图5-202所示;

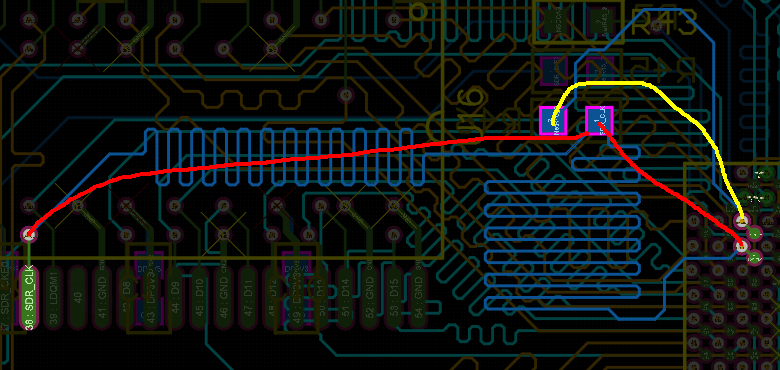

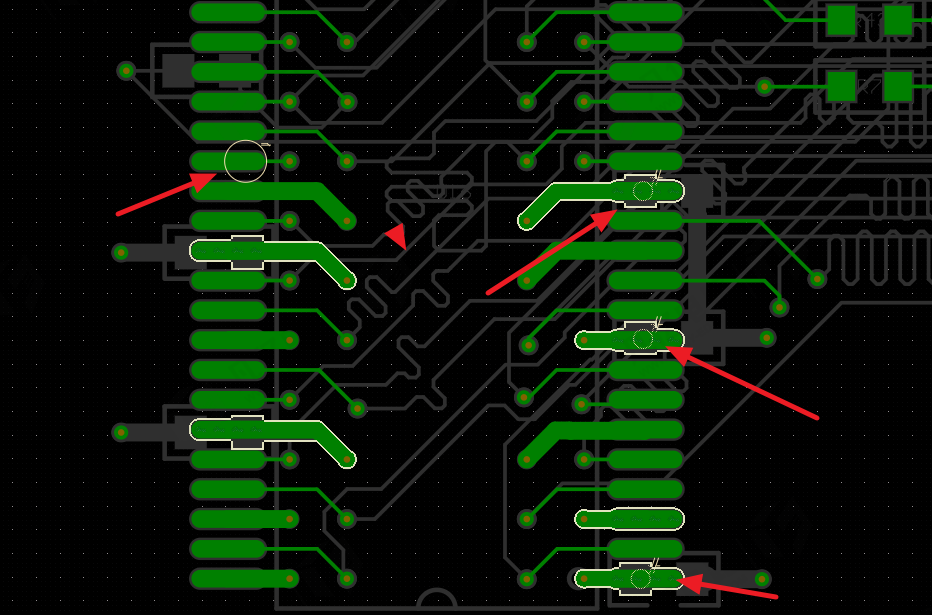

时钟线等长错误等长过于松散不齐整,绕线不均匀,锯齿状绕线尽量咬合电源信号的电容放置不均匀,尽量做到均匀的放置电容电容应尽量靠近管脚放置,不要拉出来太远以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链

1、存在开路和短路。2、地址线的等长是ic到ddr的长度。3、时钟线布线错误,应该从u16到r46再到u1。4、时钟线等长错误,是SDRAM段到电阻和电阻段ic的线一样长。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

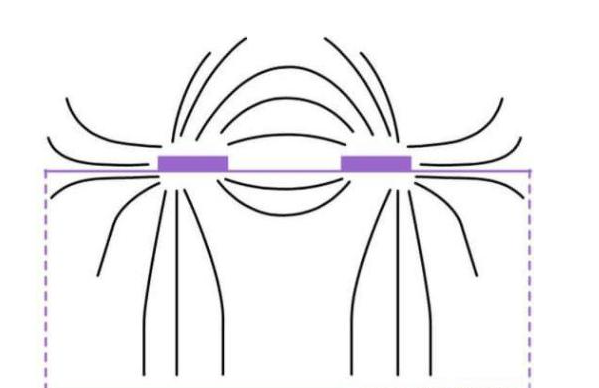

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。 串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对

Cadence Allegro单个元器件的PCB封装更新操作在PCB设计中如何对同一种类型的元器件进行封装的更新,有时候会出现这样的情况,出现错误的操作,误删除的其中一个器件的丝印或者是什么的,能否只更新这一个器件呢,其它的不进行更新,当然

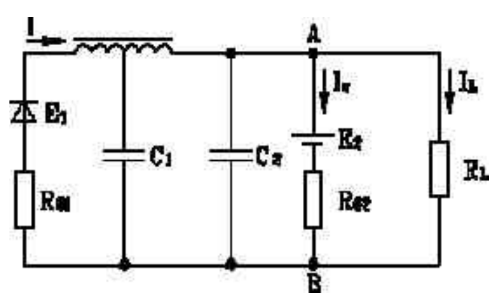

蓄电池作为汽车常见的供电设备,一直以来是人们日常生活中需要进行维护保养的存在,但由于使用操作不当或维护措施错误导致蓄电池使用寿命大大减短,还有明显的安全隐患,那么如何正确延长蓄电池的使用寿命?1、保持蓄电池处于良好的浮充状态决定电池的寿命主

扫码关注

扫码关注