- 全部

- 默认排序

电磁兼容试验中的重要内容就是骚扰发射试验。因此,控制骚扰发射是一项重要的设计内容。为了控制骚扰发射,首先要找到骚扰源,然后采取措施消除它,或者截断它发射骚扰能量的路径。 EMI骚扰源有啥特征呢?以往广泛流传的是:高电压,大电流就是骚扰源。这种说法其实很片面。单纯的一个很高的电压,或者一个很大的电流,

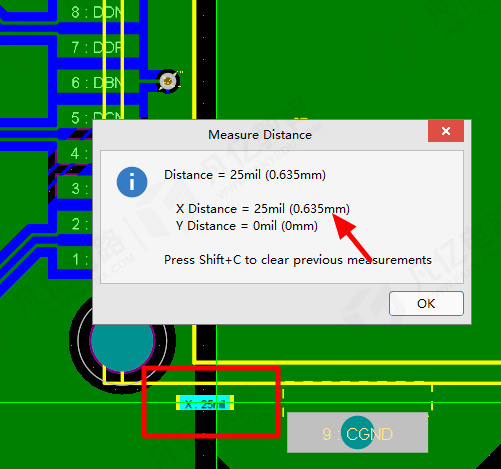

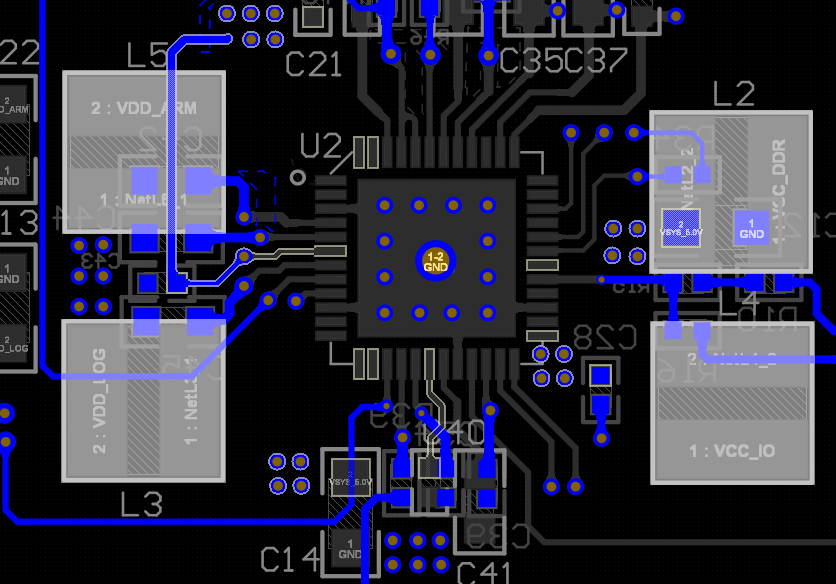

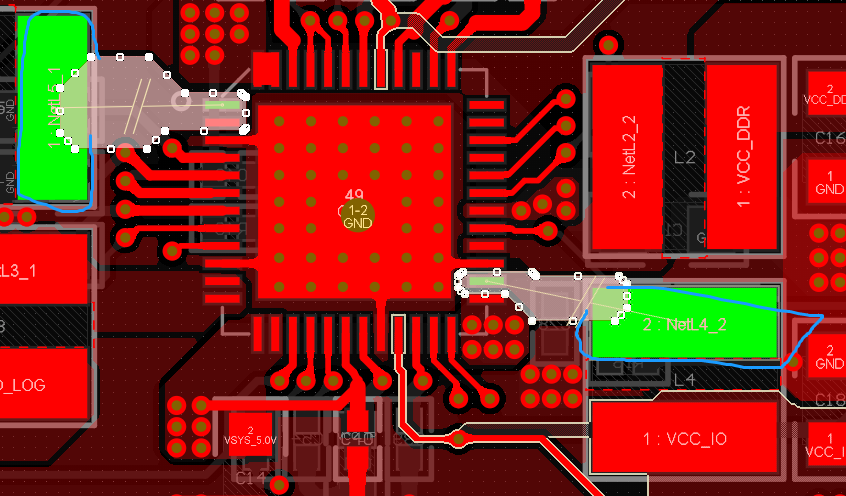

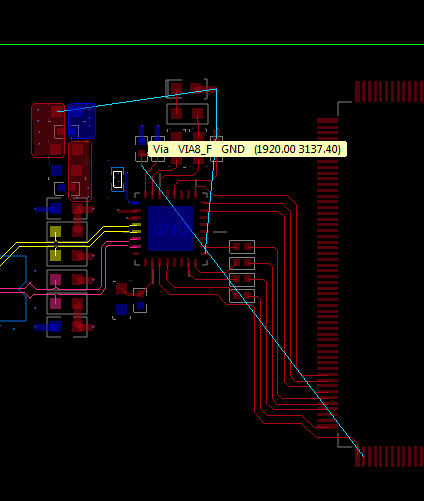

cgnd到gnd分割距离要2mm以上cgnd到gnd跨接处,两端多打过孔底层gnd铜皮被走线分割,导致多处孤岛铜皮,两层板尽量走线在一层,留一个尽量短的回流路径过孔不要上小器件焊盘多处尖岬铜皮等长绕线不要绕出直角以上评审报告来源于凡亿教育9

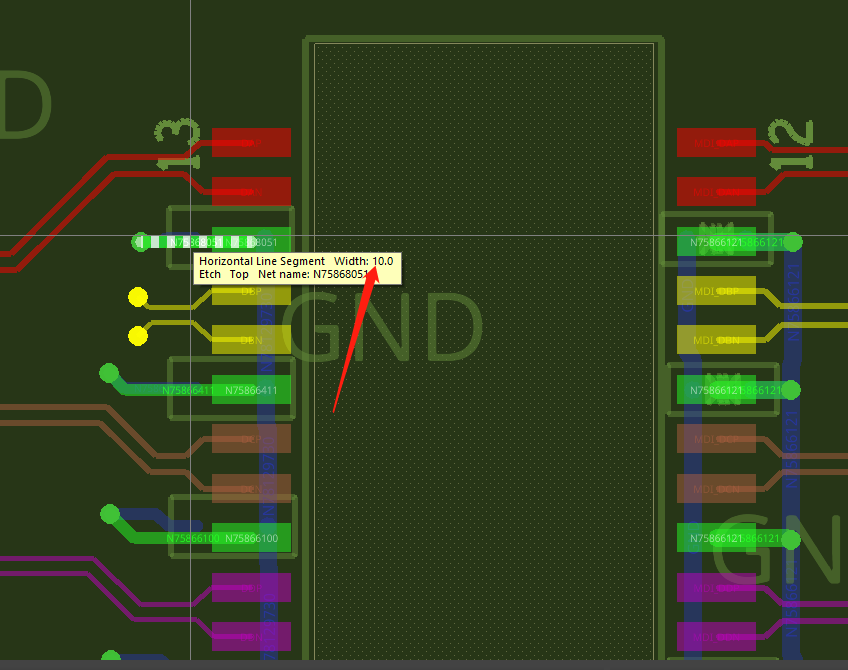

网口除差分信号外,其他的都需要加粗到20mil2.差分信号需要进行对内等长,误差5mil3.存在多处开路4.焊盘尽量从四个角出线,后期自己优化一下5.地焊盘需要就近打孔,缩短回流路径6.焊盘出现不规范,焊盘中心出线至外部才能拐线处理,避免生

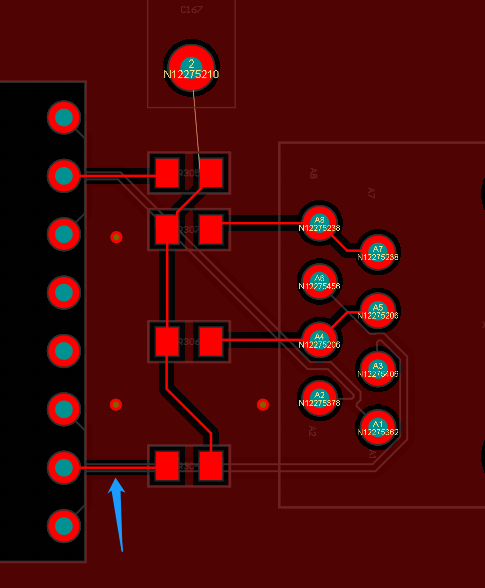

电容按照先大后小原则放置,过孔打在最后一个电容后方输入电源过孔打在第一个器件前方反馈信号过孔走线没有信号电源主输出路径没有连接,应从Q2器件铺铜连接到大电感过孔尺寸过大,常用过孔尺寸一般是8-16、10-20等除散热孔外其他过孔盖油处理以上

电感底部不要放置器件,优化下布局:电感内部的铜皮需要挖掉:信号走线不能从电阻电容内部穿过,优化下走线路径:整体需要特别处理的就是电感底部的电容,不能放在电感底部,需要优化布局。其他的DCDC以及LDO没什么问题。以上评审报告来源于凡亿教育9

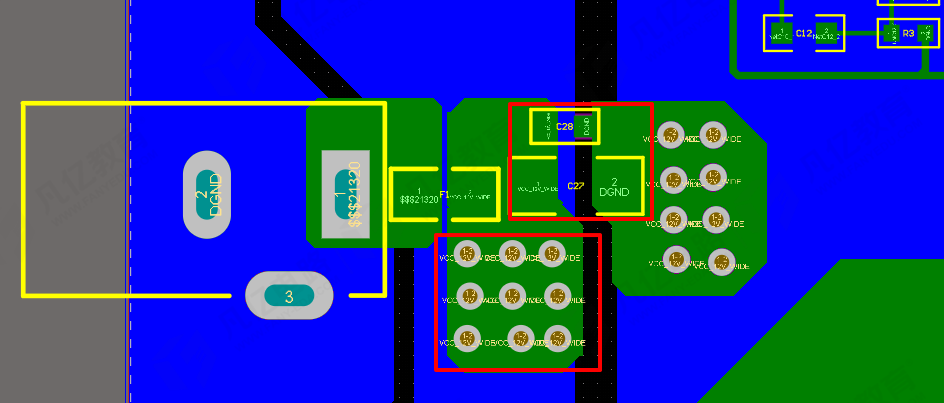

注意变压器除差分信号外,其他信号走线需要加粗处理2.电容尽量靠近管脚均匀摆放3.地网络需要就近打孔,连接到地平面4.注意晶振需要包地处理5.走线间距太近,后期容易造成短路,自己后期优化一下走线路径6.走线等长线之间需要满足3W规则7.时钟信

差分信号打孔换层 注意两侧打上地过孔,缩短回流路径:注意器件尽量整体中心对齐:过孔注意间距,不要造成平面割裂:变压器上除了差分信号 其他的加粗20MIL:差分对内等长误差控制在5MIL:RX TX需要对内做等长以上评审报告来源于凡亿教育90

铺铜尽量包裹住焊盘,容易造成开路2.注意不要存在stub线头3.反馈线宽尽量走10mil以上4.电感下面尽量不要放置器件和走线5.焊盘和走线间距过近,后期自己优化一下走线路径

电子人都知道,电子产品的设计必须遵循抗静电放电(ESD)设计规则,以此让设备处在最佳运行状态,竞争力最大化。如果是电子机箱,该如何设计,才能达到抗ESD的目的?1、确保电子设备与下列各项之间的路径长度超过20 mm。包括接缝、通风口和安装孔

还存在飞线,注意电源信号处理:差分打孔换层的过孔两边注意添加地过孔,缩短回流路径:注意差分对内等长误差为5MIL:差分组跟组不用等长,组内等长就可以了:单端信号的TX RX需要组内等长,没有设置:自己后期去设置下组内等长,在拉等长。以上评审

扫码关注

扫码关注