- 全部

- 默认排序

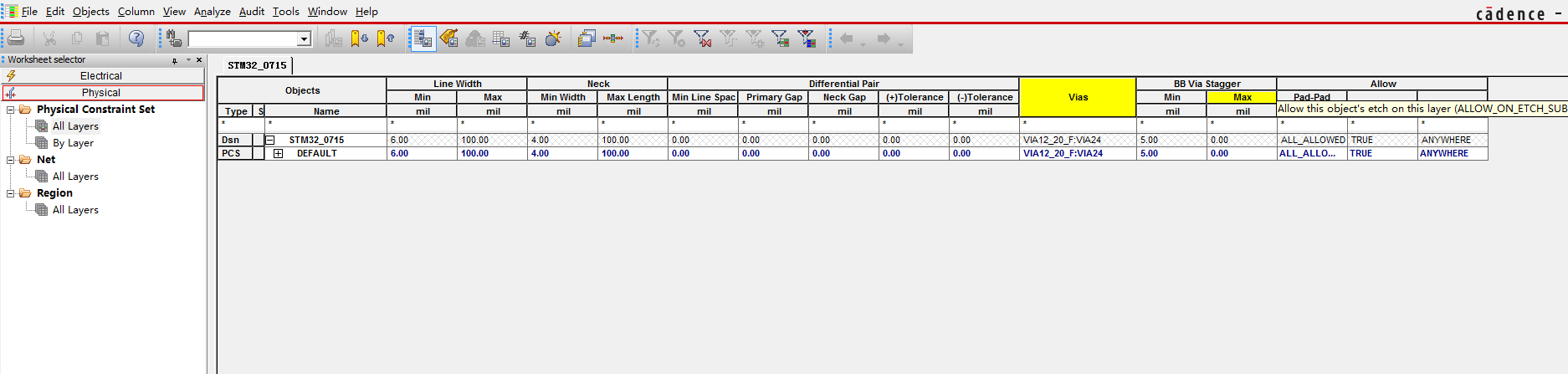

物理约束规则介绍

物理规则包括设置线宽和指定过孔库等的属性规则,在设置规则之前,需要把层叠等参数设置好。默认的为default规则。Default规则是指铺铜的单线50Ω阻抗的信号线规则,通常需要设置以下参数。(1)Line width:线宽根据阻抗计算结构进行设置,Min问默认线宽,Max为允许的最大线宽,默认为0表示不限制最大线宽,通常Min的数值不小于4mil。

蛇形天线设计技巧

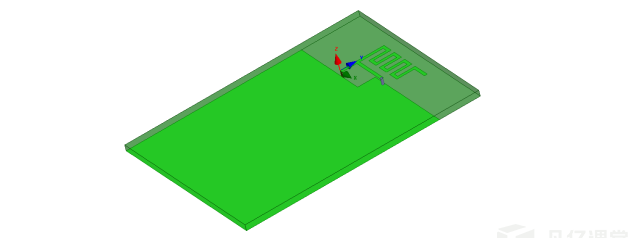

蛇形天线相信大部分朋友看到的最为广泛一种天线结构,主要应用在蓝牙、wifi、zigbee等领域。 之前有很多朋友问过我蛇形天线如何设计,比如:蛇形天线的弯折有没有什么讲究,弯折多少次合适等,其实,如果朋友们有这样的疑问,那就说明大家对蛇形天线的认识进入了一个误区,为什么这么说,因为蛇形天线本身并没有所谓“弯折规则”之类的说法,换句话说,蛇形天线的弯折都是随性的,根据每个项目的具体需要来决定,蛇形弯折有一种专业术语叫做“曲流技术”,相信很多朋友都听说过,它的目的就是使天线小型化。

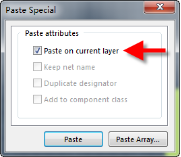

一般不规则的焊盘被称为异型焊盘,典型的有金手指、大型的器件焊盘或者板子上需要添加特殊形状的铜箔(可以制作一个特殊封装代替)。如图27所示,此处我们以一个锅仔片为例进行说明。

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

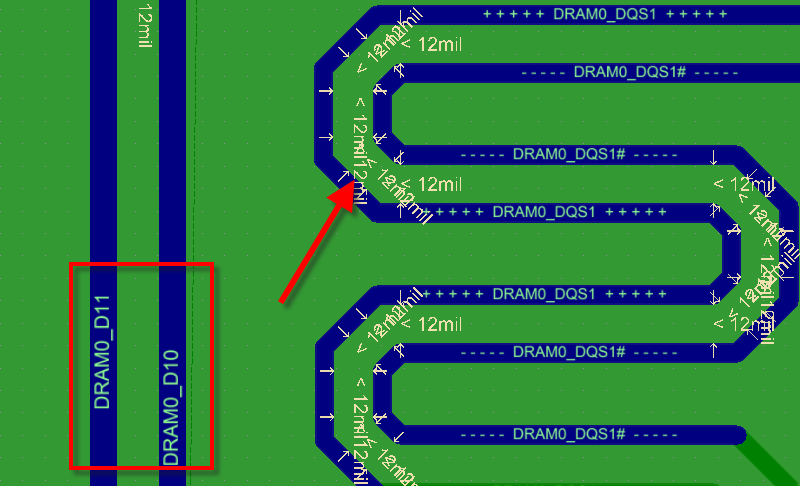

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

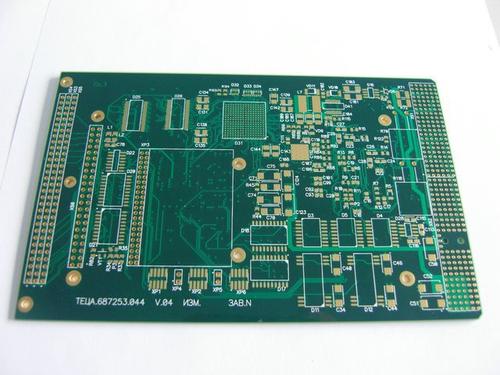

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

此Altium Designer视频是专门针对 DDR3 设计来的,采用飞思卡尔 IMX6 主控芯片, 4 片 DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,一个大 T 点两个小 T 点的方式。讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然。

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

一、8 层 Allegro T 点星型拓核心板课程详情这个是一个非常经典的 T 点星型拓核心板设计,主要采用飞思卡尔 IMX6 主控芯片,4 片DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等。

电气(Electrical)规则设置是设置电路板在布线时必须遵守的规则,包括安全距离、开路、短路方面的设置。这几个参数的设置会影响所设计PCB的生产成本、设计难度及设计的准确性,应严谨对待。

扫码关注

扫码关注