- 全部

- 默认排序

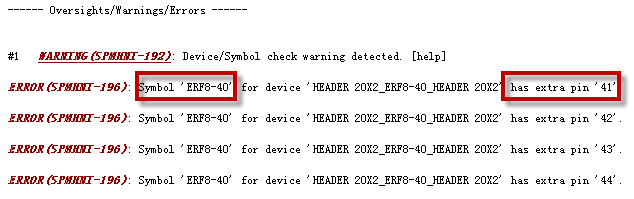

请问这种错误要怎么解决,按工具里的复位错误标志可以取消,但在最后检查时还是会报错,来回导入好几次都是这样,怎么解决,求解答

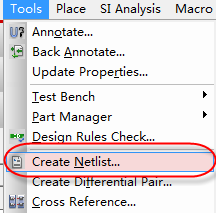

用Design Entry CIS生成逻辑网表的时候没有报错,能够成功的生成pxlBA.txt,netlist.log,pstchip.dat,pstxnet.dat,pstxprt.dat五个文件,这五个文件在同一个文件夹NetList下。然后一个叫work2的文件夹使用PCB Design GX

一个学习信号完整性仿真的layout工程师作为layout工程师,首先的输入条件就是原理图,也就是常说的(原理图导出网表文件)网表文件,有硬件工程师会直接把网表发给我们,有的直接给我们dsn文件,要求我们自己导出导入网表,下面简单介绍导出导

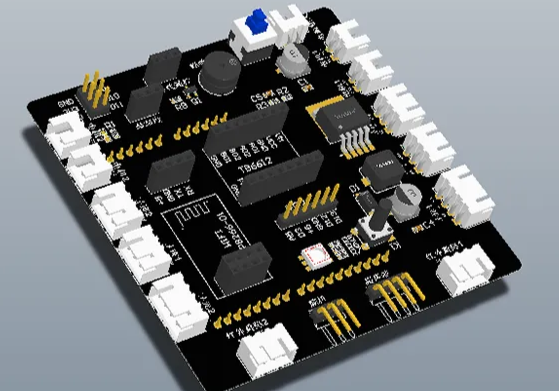

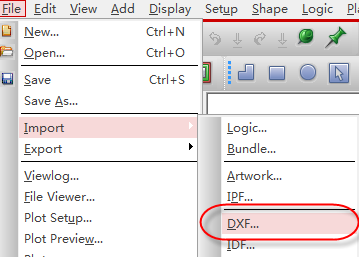

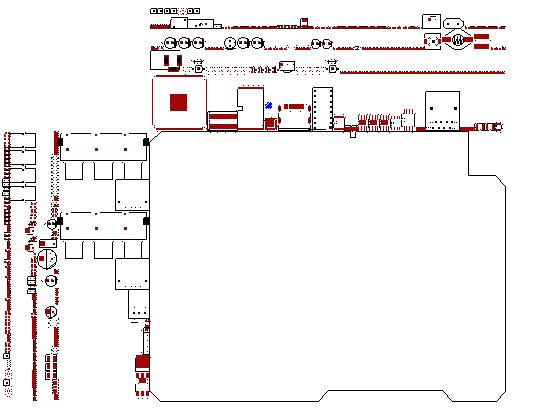

答:我们在进行PCB设计之前,除了将原理图的网表导入,将元器件放置在PCB板上,还需要做的就是将结构文件导入到PCB中,进行结构器件的定位。这里呢,我们详细讲解一下结构文件如何导入到PCB中,具体操作如下:

答:很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:

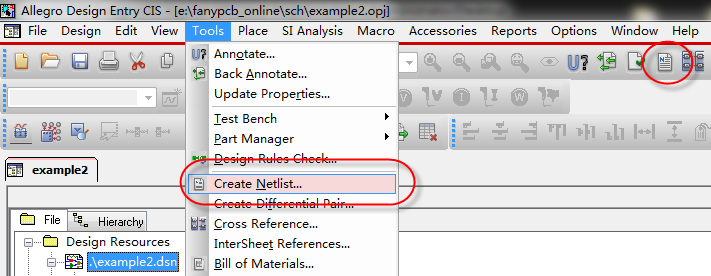

答:现在市面上用的最多的是,Orcad软件绘制原理图,Allegro软件绘制PCB版图。我们现在讲解一下怎么使用Orcad软件将绘制好的原理图,输出第一方的网表,然后将第一方的网表导入到Allegro软件中,具体操作如下:

答:Allegro的第一方网表与第三方网表有以下几个区别点;与Allegro实现交互式操作的是第一方网表,第三方网表时不可以实现交互式操作;第三方网表不能将器件的Value属性导入到PCB中,输出时以封装属性来代替Value属性,第一方网表是可以的;网表导入到PCB中时,第三方的网表需要指定事先指定好PCB封装库文件,并产生Device文件,才可以将网表导入到PCB中,第一方网表则可以直接导入。

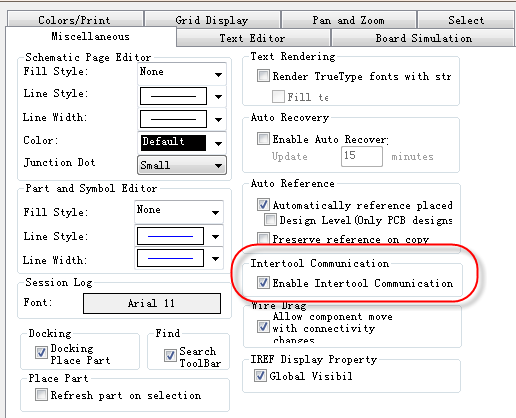

在前面的问答中,我们分别详细讲述了第一方网表与第三方网表的输出方法与导入方法,这两种导入方法有什么区别与联系呢,是不是都可以呢?这里呢,我们讲解一下第一方网表与第三方网表的区别与联系,具体如下:首先,如果是在Allegro软件中导入的是第一方网表,是可以进行同步操作的,导入的第三方网表,是不可以进行不同操作的,第一方网表导入的时候,需要进行同步操作都设置在原理图设置下,如图6-34所示,将第二个选项勾上即可; 图6-34 同步操作设置示意图其次,Allegro软件的第一方网

扫码关注

扫码关注