- 全部

- 默认排序

Orcad是兼容很好的原理图设计工具,很多芯片原厂习惯性用这个软件来进行原理图设计,但是有时候PADS工程师来进行PCB设计的时候就不好直接导入了,那这个时候需要用到网表的输出 和导入了,为了使读者更加具体的学会这个技能,我们龙老师录制了此分技巧视频,方便大家学习

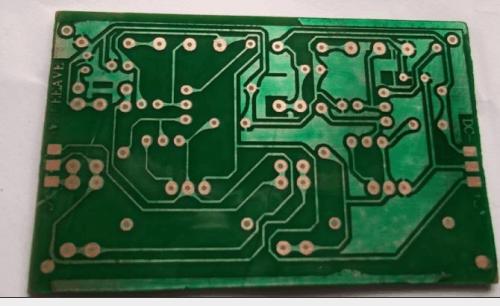

一、2 层 Allegro stm32 最小系统主板课程详情这个是一个非常经典的 2 层 stm32 最小系统主板实战,以最常见的的 STM32 主芯片为核心,录制入门级的 STM32 最小系统板电子设计的实战视频,全程讲解原理图封装库的绘制、原理图的绘制、网表导入、PCB 封装调用、PCB 布局、PCB 布线、PCB 检查、光绘输出、光绘检查、文档归档。

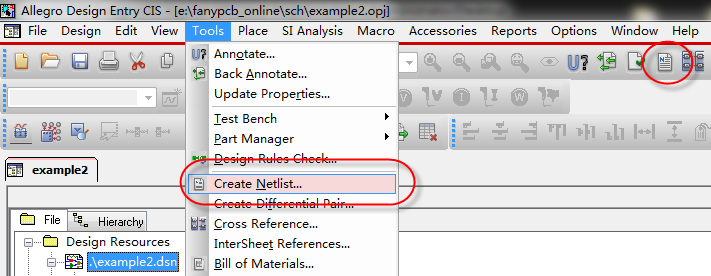

现在市面上用的最多的是,Orcad软件绘制原理图,Allegro软件绘制PCB版图。我们现在讲解一下怎么使用Orcad软件将绘制好的原理图,输出第一方的网表,然后将第一方的网表导入到Allegro软件中,具体操作如下:第一步,选中原理图根目录,执行菜单命令Tools-Create Netlist,创建网表,如图6-26所示; 图6-26 使用Orcad软件创建第一方网表示意图第二步,执行上述命令之后,会弹出如图6-27所示的界面,在此界面中选择PCB Editor,进行第一

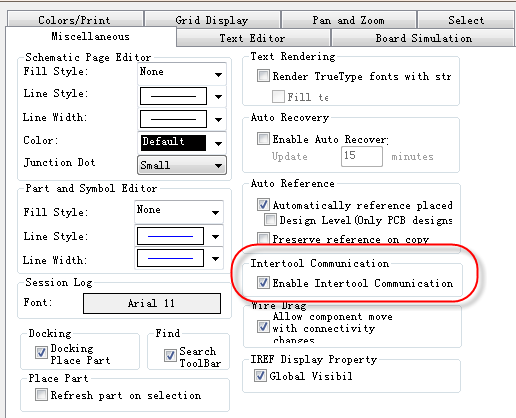

在前面的问答中,我们分别详细讲述了第一方网表与第三方网表的输出方法与导入方法,这两种导入方法有什么区别与联系呢,是不是都可以呢?这里呢,我们讲解一下第一方网表与第三方网表的区别与联系,具体如下:首先,如果是在Allegro软件中导入的是第一方网表,是可以进行同步操作的,导入的第三方网表,是不可以进行不同操作的,第一方网表导入的时候,需要进行同步操作都设置在原理图设置下,如图6-34所示,将第二个选项勾上即可; 图6-34 同步操作设置示意图其次,Allegro软件的第一方网

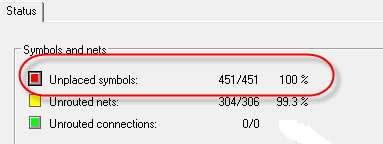

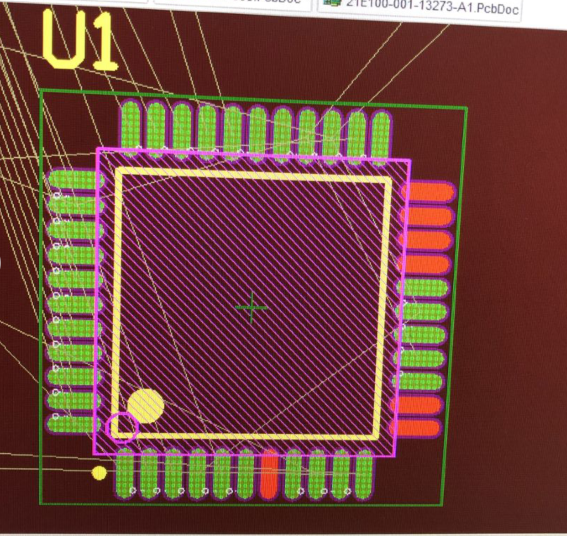

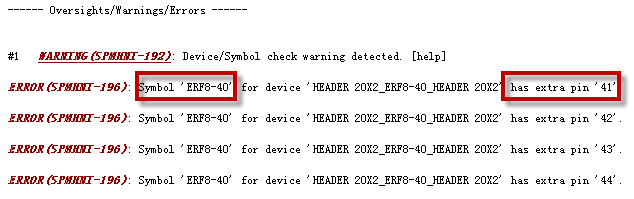

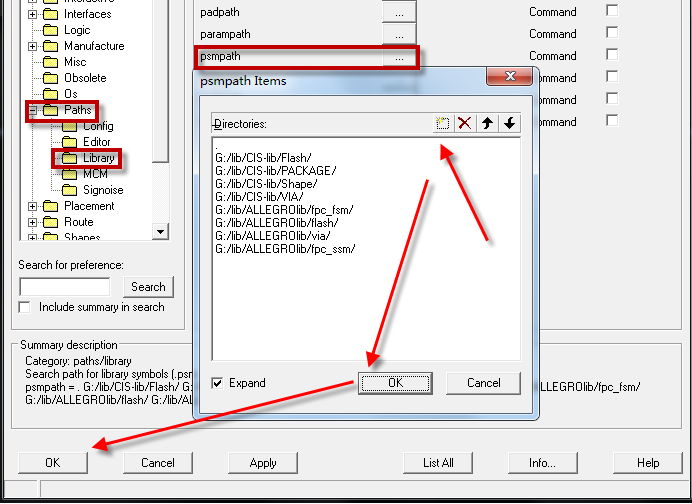

很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:第一步,需要检查原理图的网表是否导入成功,执行菜单命令Display,在下拉菜单中选择Status,整个PCB文件的状态,如图324-1所示,进入到状态的界面,最上面一栏是Symbols and nets的选项,网表导入成功

答:Allegro的第一方网表与第三方网表有以下几个区别点;与Allegro实现交互式操作的是第一方网表,第三方网表时不可以实现交互式操作;第三方网表不能将器件的Value属性导入到PCB中,输出时以封装属性来代替Value属性,第一方网表是可以的;网表导入到PCB中时,第三方的网表需要指定事先指定好PCB封装库文件,并产生Device文件,才可以将网表导入到PCB中,第一方网表则可以直接导入。

扫码关注

扫码关注