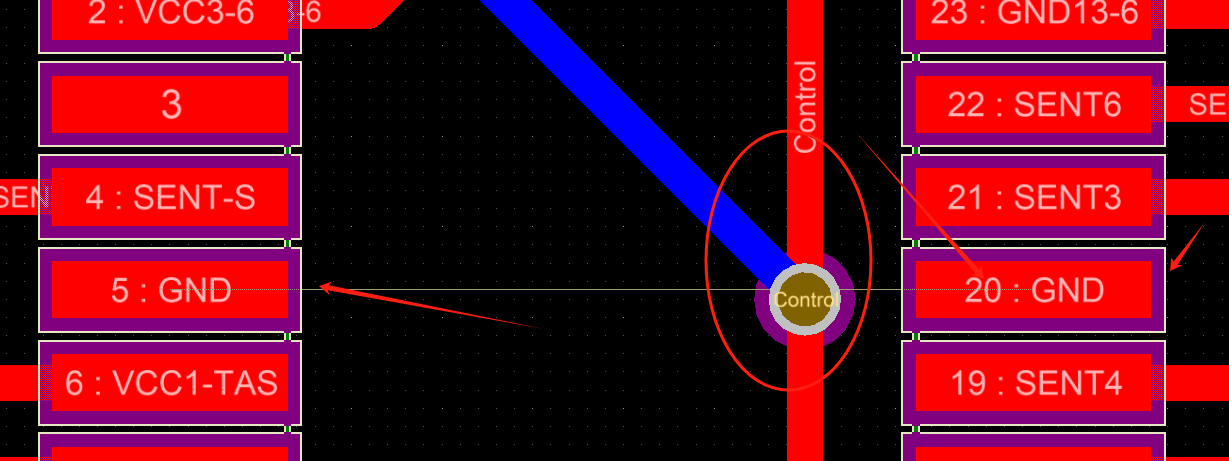

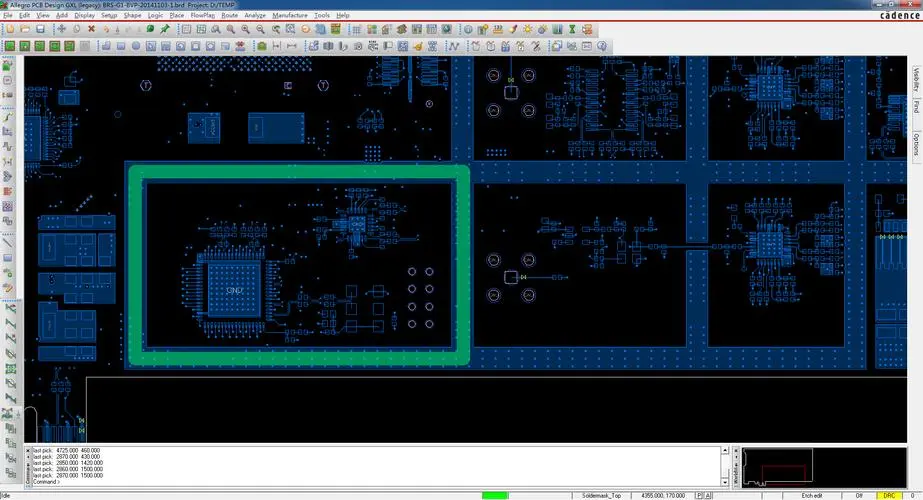

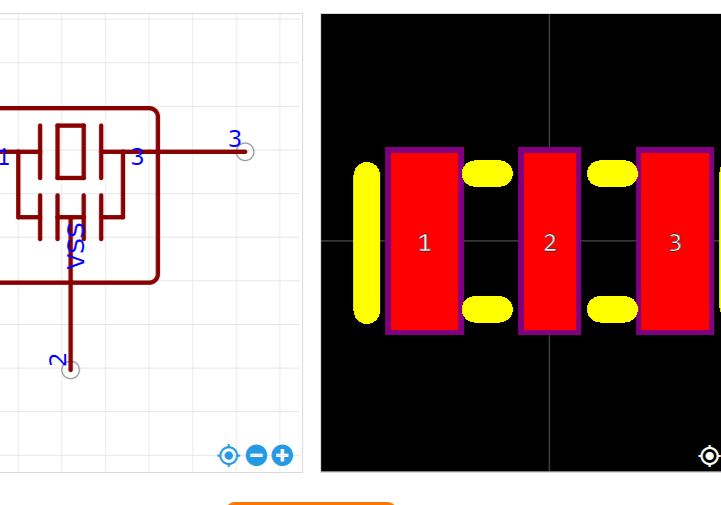

用Design Entry CIS生成逻辑网表的时候没有报错,能够成功的生成pxlBA.txt,netlist.log,pstchip.dat,pstxnet.dat,pstxprt.dat五个文件,这五个文件在同一个文件夹NetList下。然后一个叫work2的文件夹使用PCB Design GXL(legacy)建了一个板子并导入逻辑网表,导入失败且提示“work2/netrev.lst“dose not exist,也就是说,程序无法正常生成netrev.lst文件,然后点place放置元件,其中一个元件都没有,请问这是怎么回事?要如何解决?

扫码关注

扫码关注