- 全部

- 默认排序

1、VDD_NPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VDD_NPU的电源在外围换层时,要尽可能的多打电源过孔(7个以

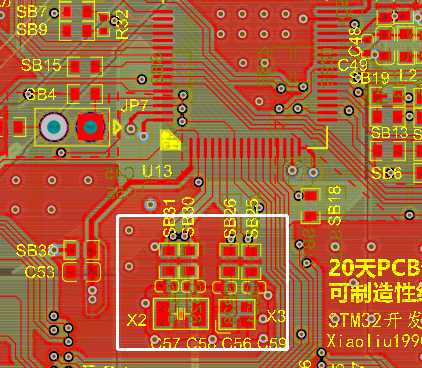

还存在较多飞线,基本上是电源以及地没有连接:电源主干道器件尽量靠近管脚,不要间隔那么远,主干道器件优先级最高,其他的配置电阻电容可以调整的:电源输出的反馈信号也没有连接:器件尽量整体中心对齐处理下:此处电源连接的线宽完全满足不了载流大小,需

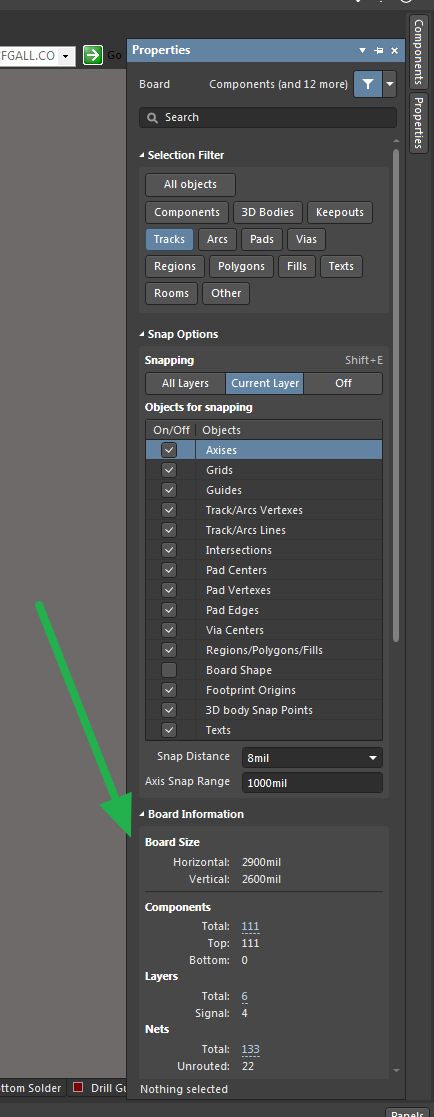

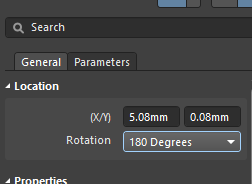

Ad19由于做了更新的改动,所以我们对应的RB就不能进行管脚的查看,首先我们点击我的PCB界面,然后我们点击我们的PCB的空白处,我们点击一下,然后我们对应在我们的panel 面板下面调用出我们的proprieties这个界面,这个和低版本不一样之处在于,高版本将prorieties这个界面替代了我们的PCB Inspertor.

装了Altiumdesigner17有一段时间了,最近在打印原理图的时候,出了一些问题,无论是打印还是smart pdf 打印出来的原理图,原理图中所有元件有一半的管脚名都不会显示出来。软刚装好的时候是正常的,把工程拷贝到另一台装有AD17的电脑上打印预览是正常的,然后我又重装了一边AD17,问题依

存在开路2.此处走线可以在进行一下优化3.器件摆放尽量中心对齐处理4.一层连接可以不用打孔5.差分需要进行对内等长,误差5mil6.ESD器件尽量靠近管脚摆放7.后期自己把电源和地再平面层处理一下,添加上网络以上评审报告来源于凡亿教育90天

晶振可以在靠近管脚一些。差分锯齿等长不要大于两倍间距散热过孔正反都要开窗处理走线不满足3w间距这里输出要加粗处理电容按先大后小放置走线不要穿过电容电阻

在logic软件当中制作CAE封装,对于管脚少的器件可以手动的输入管脚名称和编号,但对于一些管脚特别多的器件可以利用导入CSV文件的方式,一次性把管脚信息全部导入,节省了我们制作封装的时间。

扫码关注

扫码关注