- 全部

- 默认排序

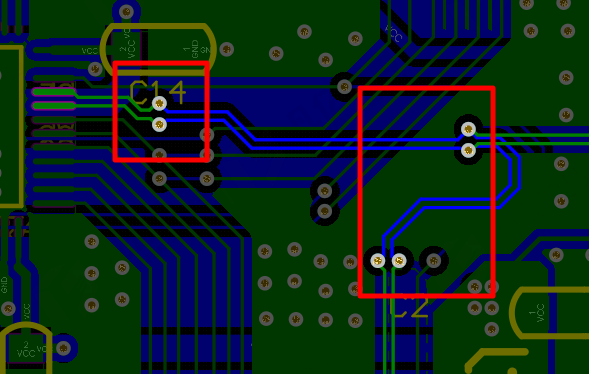

差分对尽量少换层差分对内等长误差5mil232模块C+,C-;V+,V-所接的电容属于升压电容,注意布 局尽量靠近,走线加粗。sd卡模块数据线整组包地处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

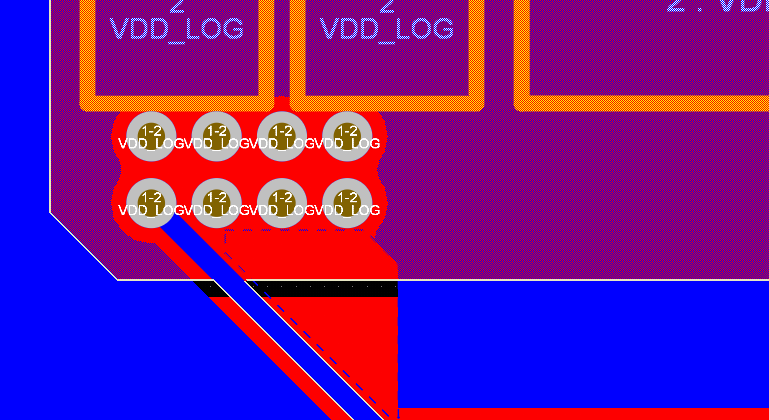

这里底层也要铺铜这两个过孔没有和底层连接没有必要打的这个走线也是没有必要拉出来的,这样形成天线会有干扰以上评审报告来源于凡亿教育AD弟子计划特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taob

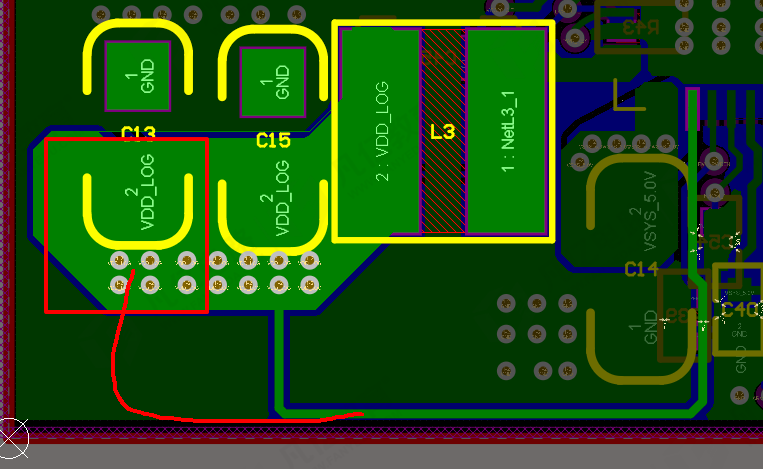

还存在开路报错,自己检查修改下:电感当前层的内部注意放置挖空区域:注意主干道器件需要整体中心对齐,都没 对齐:根据电流输出方向,电容按照先大后小的顺序布局,布局有问题:器件丝印位号没有放置整齐,要不在板外,要不就丝印重叠或者丝印覆盖焊盘了,

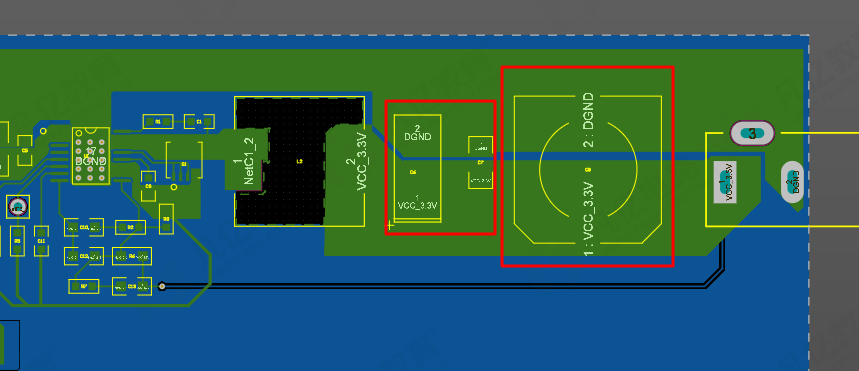

器件遵循先大后小原则摆放,大电容放到前面小电容放大电容后相邻电路电感应朝不同方向垂直放置焊盘出线避免从长边、四角出线,铺铜、走线尽量避免直角锐角器件尽量中心对齐,相邻器件尽量朝一个方向放置以上评审报告来源于凡亿教育90天高速PCB特训班作业

5G可以帮助实现模块化工厂的理想,在模块化工厂中,机器可以快速重新配置,以优化生产。对于制造商来说,5G提供了改善运营性能和增强流程弹性的绝佳机会。许多新的服务和机会将来自于其无处不在的连通性。这句话出自美国制造业研究所发布的一份报告,该报

答:在前面的几个问答当中,我们都有提到,对一些做好的模块进行创建Groups组的操作,方便我们进行模块复用、布局操作。我们创建了Groups组之后呢,这个属性会一直存在,我们是否可以将这个属性给去除掉,方便后期的布线操作与规划。因为添加了这个Groups组的属性以后,从这个模块走出的线会出现下面的小方块的现象,如图6-22所示,虽然不影响整体的性能,但是影响美观,所以呢,这里我们会讲解一下如何将已经创建好的Groups组进行打散的操作,具体操作如下:

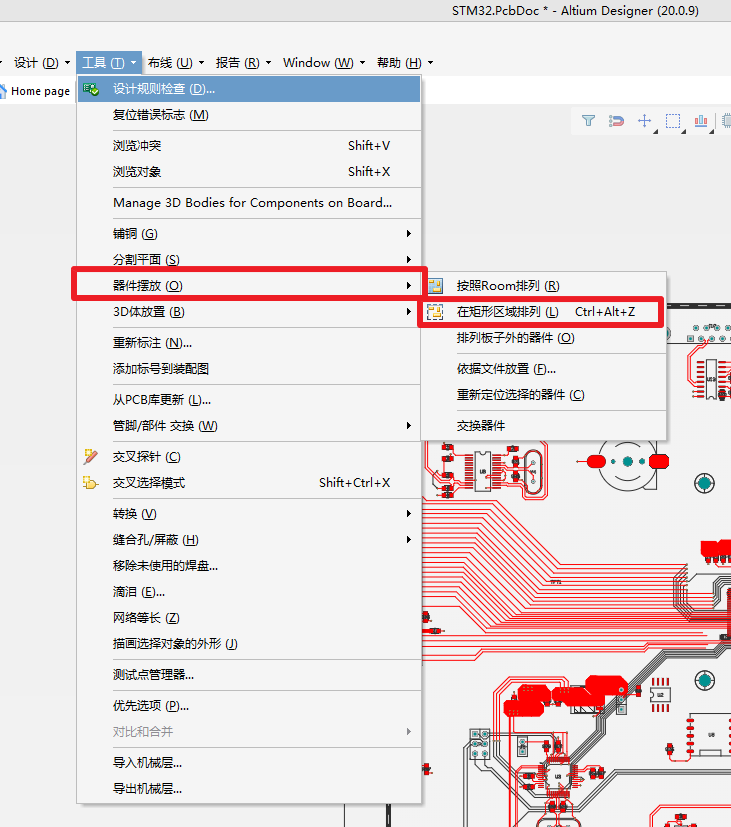

在这里介绍一个元件排列的功能,即在矩形区域排列,可以在布局初期结合元件的交互,方便的把一堆杂乱的元件按模块分开并摆放在一定的区域内。

本课程介绍了FPGA SDRAM文档的阅读和理解、SDRAM的功能汇总、SDRAM的实现架构、SDRAM接口的模块划分、SDRAM的时序分析和约束。

我们在Altium Designer原理图中,选中了某个元件或者某个模块电路,只要是被选中的,都会被一种颜色给框选包裹起来。如果我们想去改变这个颜色,那么怎么去操作呢?今天就来讲讲这个操作的应用,应该怎么样去解决。

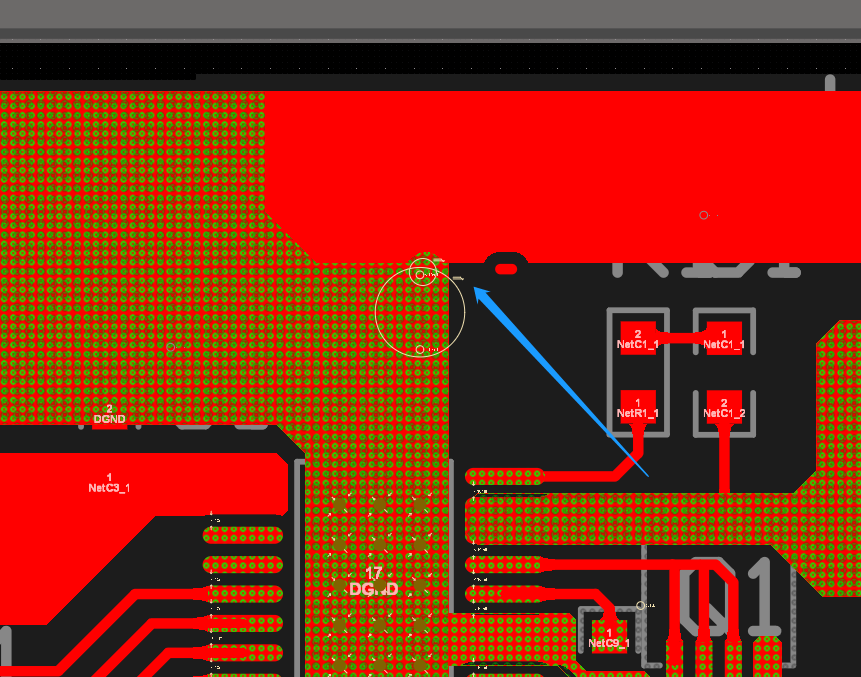

过孔打到最后一个器件后方,反馈信号连接到最后一个器件后方电源走线加粗走线同层器件中间多余铺铜挖空走线铺铜在焊盘内和焊盘保持等宽,出焊盘后尽快加粗走线多处尖岬铜皮未处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审除芯片下方散热打孔

扫码关注

扫码关注