- 全部

- 默认排序

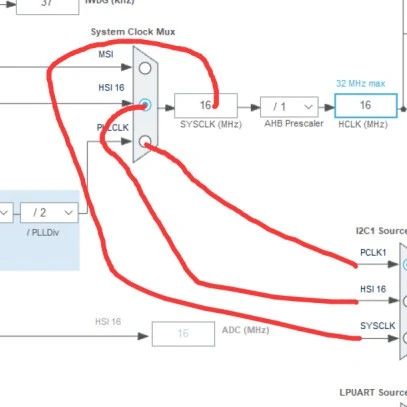

1,低速时钟LSE是外部晶振作时钟源,主要提供给实时时钟模块,所以一般采用32.768KHz。LSI是由内部RC振荡器产生,也主要提供给实时时钟模块,频率大约为40KHz。(LSE和LSI)只是提供给芯片中的RTC(实时时钟)及IWDG(独立看门狗)使用。 2,中速时钟MSI RC

作为一种精密的频率元件,单片机中的晶振却很容易出现问题,轻微的碰撞都可能导致晶振损坏,因此,遇到单片机晶振不起振是很常见的一种现象。下面就单片机晶振经常遇到的问题及处理方法为大家做一个简单的介绍。一、单片机晶振不起振的原因分析首先,我们分析

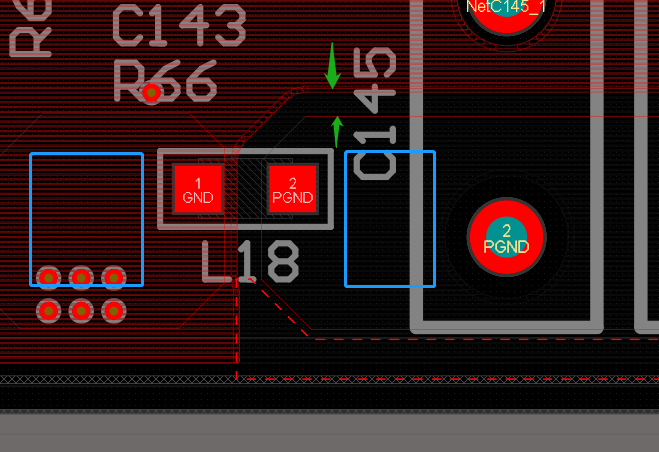

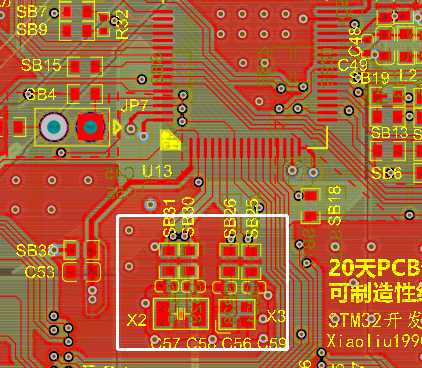

跨接器件旁边尽量多打地过孔,间距最少1.5mm2.注意差分需要进行对内等长,误差5mil3.注意差分出线要尽量耦合4.晶振下面不要走线5.地址线之间等长需要满足3W6.走线未连接到过孔中心,存在开路7.反馈需要走一根10mil的线8.器件摆

有源晶振与无源晶振的比较

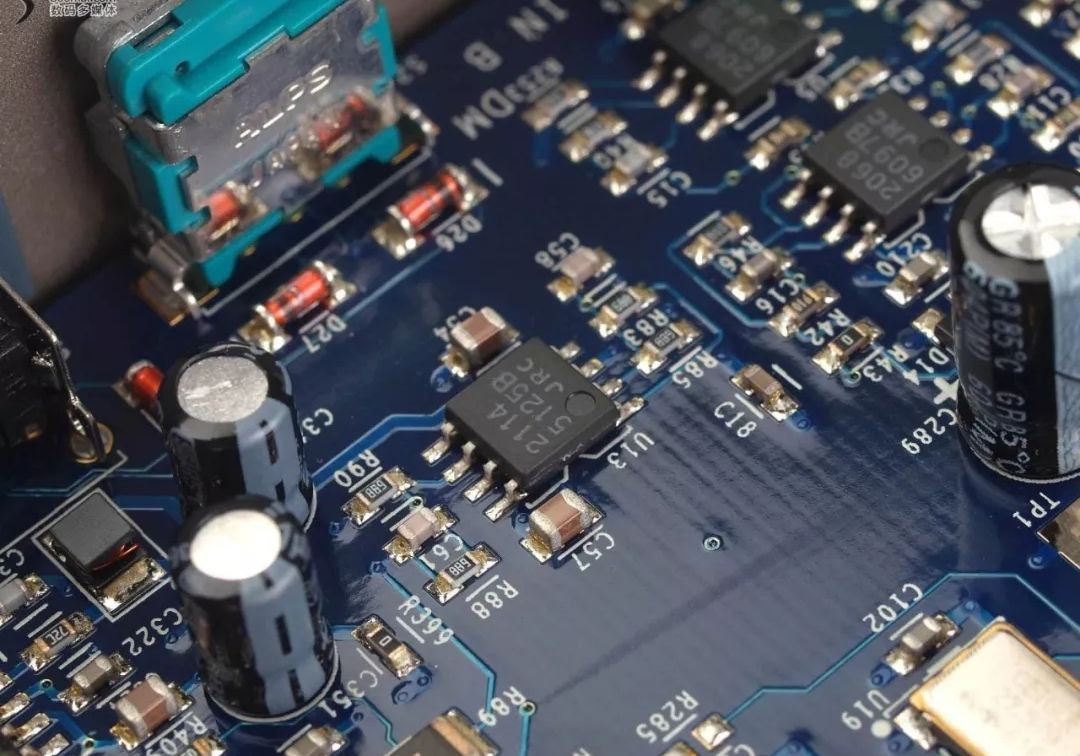

有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单(主要是做好电源滤波,通常使用一个电容和电感构成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路。

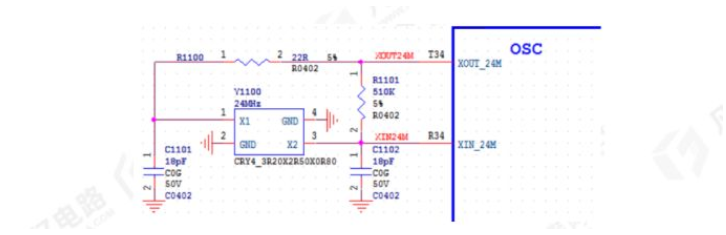

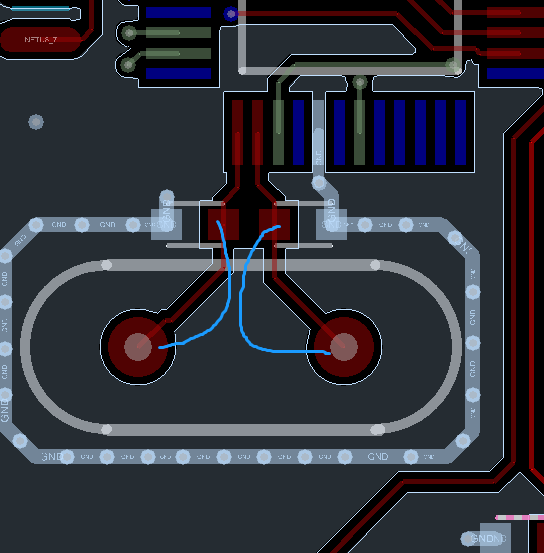

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。图1 时钟电路针对时钟电路PCB设计有以下注意事项:1、晶体

晶振走内差分需要再优化一下2.地分割间距最少满足1mm3.锯齿状等长不能超过线距的两倍4.网口除差分线外,其他的都需要加粗到20mil5.模拟信号尽量一字型布局6.电感所在层的内部需要挖空7.反馈需要从最后一个电容后面取样8.数据线和地址线

随着电子技术高速发展,振荡器种类开始繁多,但如果发现这些半导体厂商,很容易发现,相对于石英晶硅,大家都更会选择MEMS硅晶振,这是为什么?1、全自动化半导体工艺MEMS硅晶振采用先进的半导体工艺制造,实现了全自动化生产,从而避免了气密性问题

晶振可以在靠近管脚一些。差分锯齿等长不要大于两倍间距散热过孔正反都要开窗处理走线不满足3w间距这里输出要加粗处理电容按先大后小放置走线不要穿过电容电阻

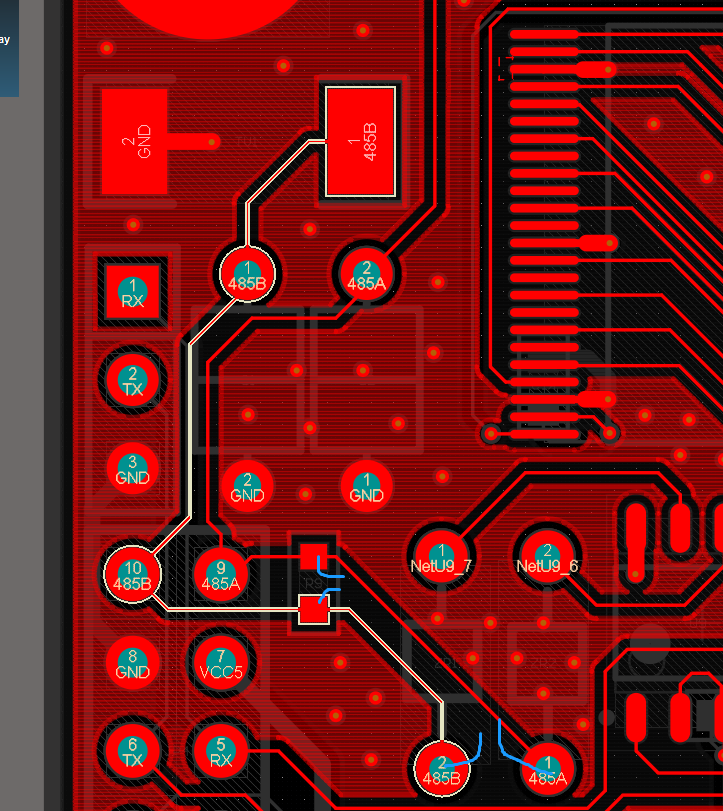

1.485信号需要走内差分处理,后期自己调整一下布局,然后重新走线2.晶振优先布局,走线路劲要尽量短3.晶振注意电容摆放顺序,先经过电容,在到晶振4.差分出线要耦合,走线尽量不要走小器件中间,容易造成短路5.差分对内等长处理不当,锯齿状等长

扫码关注

扫码关注