- 全部

- 默认排序

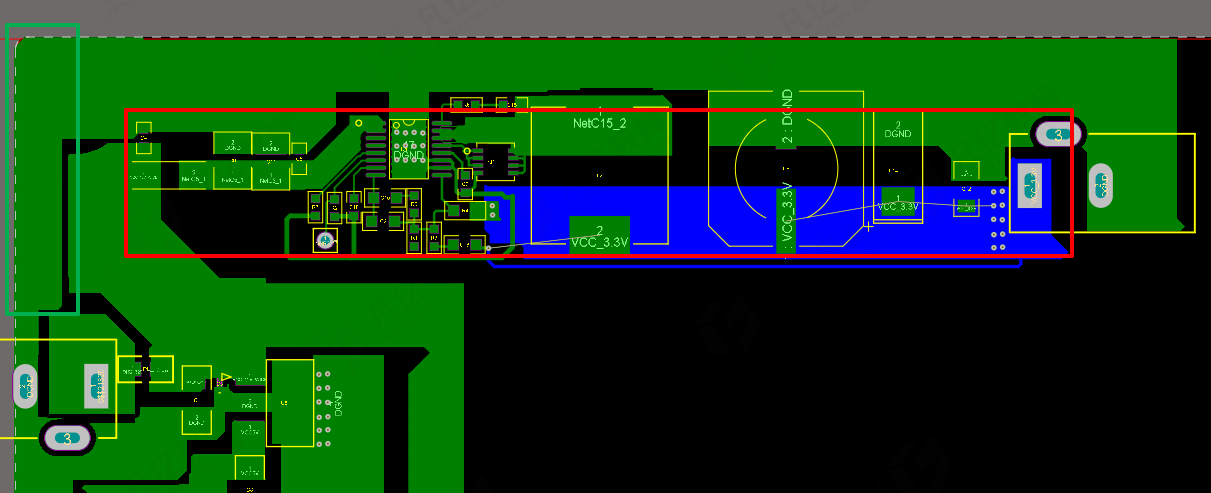

这个导入进来就是这样的,正在PCB摆放器件,规则还没改,类里面就添加了一个PWR。MCU和USB引脚都是绿色,看看是哪的问题。

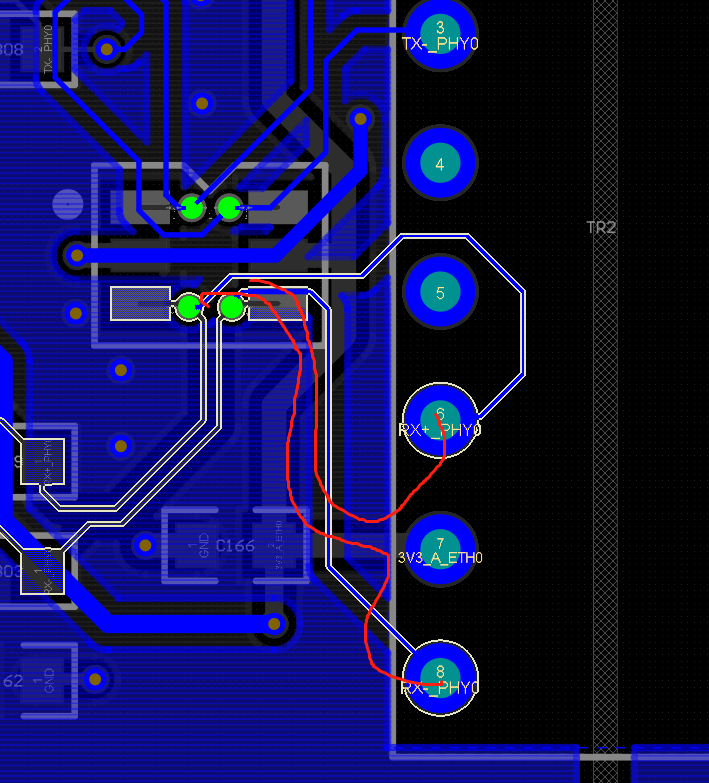

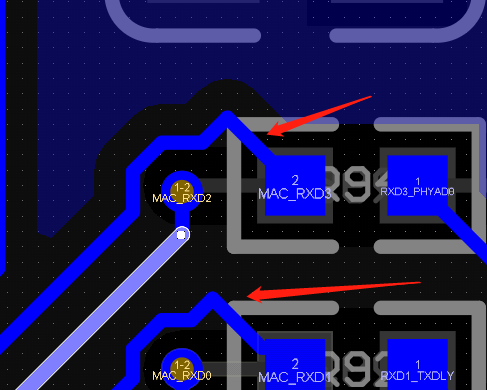

差分线要按阻抗线宽线距要求耦合走线网口到芯片的差分都需要优化,后期自己好好理解差分,然后走线需要调整一下2.器件摆放尽量中心对齐处理3.走线需要优化一下,不要有锐角4.TX分组错误5.注意等长蛇形走线尽量45度,不要直角6.除了散热过孔,其

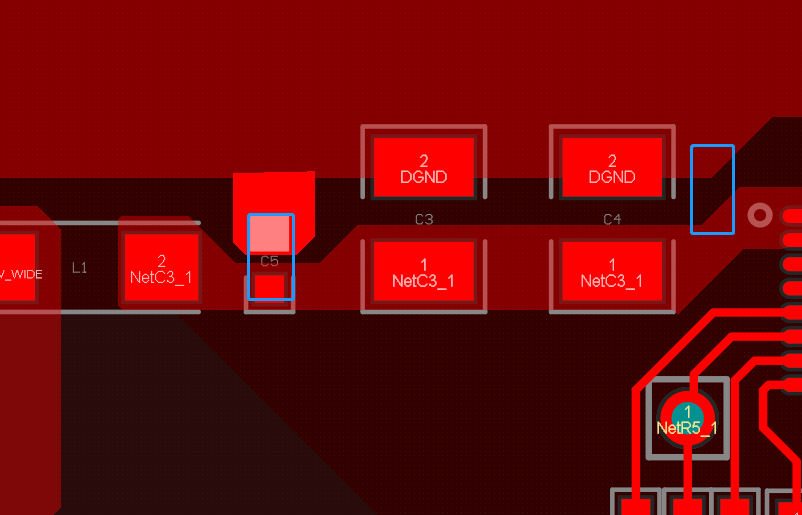

注意电容输入需要按照先大后小进行摆放2.电感所在层的内部需要挖空处理3.存在多处开路4.模块复用后需要自己对铜皮赋予网络,重新铺铜,否则会存在无网络铜皮,造成开路5.走线需要连接到焊盘中心6.除了散热过孔,其他的都需要盖油处理7.后期需要在

如图,第十三道主流程为包装。包装是整个生产流程的最后一道了,目的:显而易见,把检验合格的板子包装好后入库待发。包装相对就很简单多了,但也是有流程的,如下:1.点数。即核对上工序来料的数量。2.分方向,分数量。将产品按同一个方向摆放好,然后根

走线尽量拉直,自己优化一下2.等长线之间需要满足3W3.线宽尽量保持一致4.电容摆放尽量先经过电容在进入管脚5.跨接器件旁边尽量多大地过孔SD时钟信号尽量单根包地以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

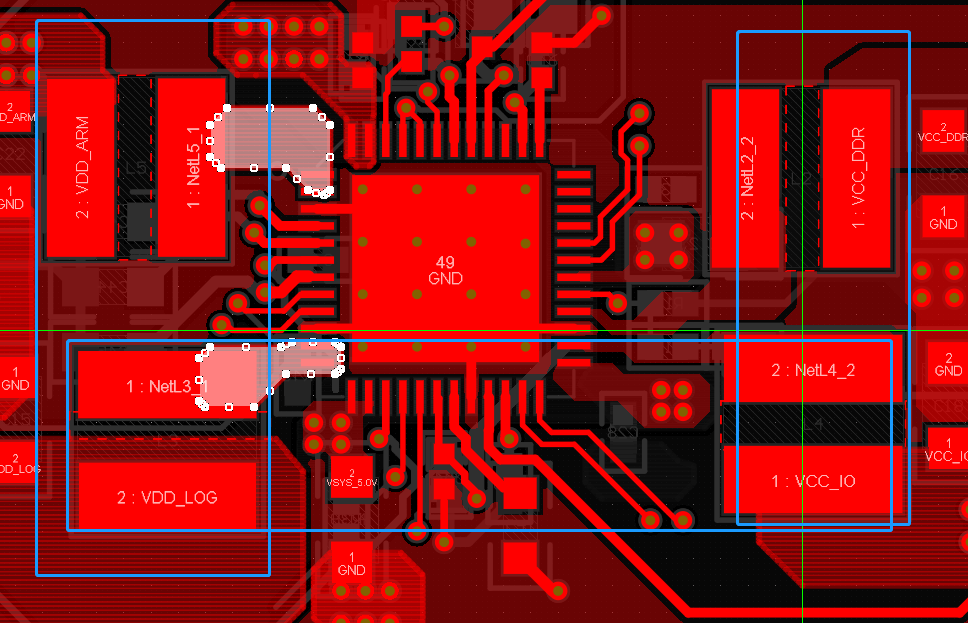

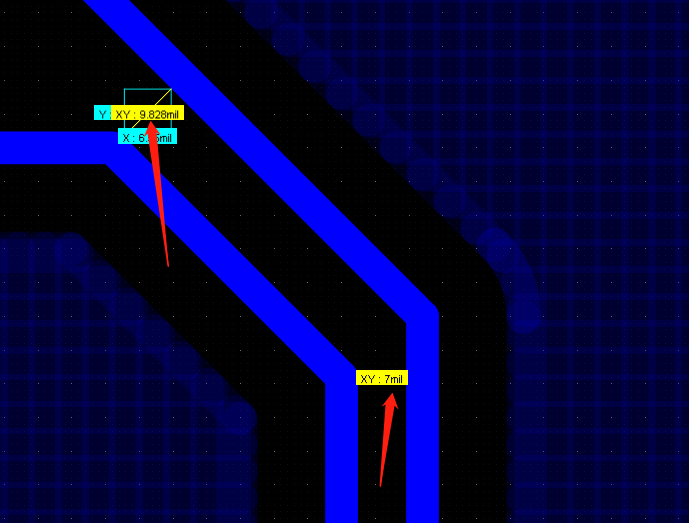

器件摆放尽量中心对齐处理2.铺铜时尽量把焊盘包裹住,这样容易造成不完全连接3.电感所在层的内部需要挖空处理4.电感下面尽量不要放置器件和走线5.反馈信号需要走10mil6.注意过孔不要上焊盘,过孔离焊盘尽量6mil以上7.除了散热过孔,其他

注意差分凸起高度不能超过线距的两倍2.差分走线需要优化一下3.时钟信号尽量包地处理4.电容尽量靠近管脚均匀摆放5.差分出线要尽量耦合,后期自己优化一下6.存在多处开路后期自己在顶底层铺上电源和地铜皮7.变压器需要挖空所有层处理

红圈内的是一整路dcdc电路,只需要这些器件地焊盘连接到一起在芯片下方打孔,不需要把整个电路板的地焊盘都一起连接焊盘避免从长边、四角出线反馈信号走线连接到dcdc电路最末端顶层焊盘没有连接铺铜走线尽量避免直角锐角器件摆放太近相互干涉电源主输

差分需要按照阻抗线距走,后期埃及调整一下2.差分对内等长凸起高度不能超过线距的两倍网口座子需要靠近板框摆放3.差分出线要尽量耦合,走线需要优化一下4.时钟信号包地需要在地线上打孔,建议50mil-100mil一个以上评审报告来源于凡亿教育9

相同的模块怎么呈圆形摆放

如图,一个圆形的板子有32个相同的模块,导入网表之后,模块复用之后怎么像图中一样,按照等分圆的方式摆放,复制led那个呈圆形摆放我知道,但是这个是所有的元件已经导入。

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注