- 全部

- 默认排序

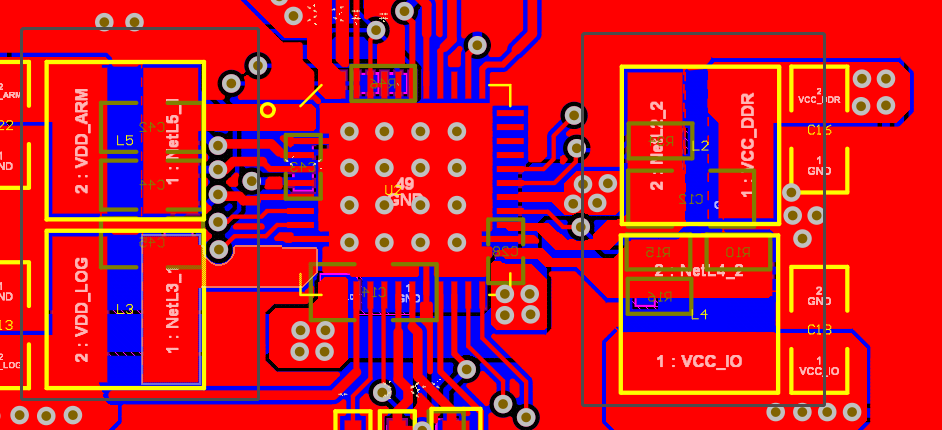

电感底部不能放置器件,建议吧电阻电容放到IC底部去,重新布局下:铺铜尽量不要直角以及尖角:类似情况的都自己修改下。电感内部要挖干净:扇孔要对齐等间距:板上这种死铜去除掉:铜皮都仔细认真绘制,把焊盘包裹上,不要很随意:焊盘扇出主意拉直出去,跟

注意电感当前层的内部铜皮挖空:焊盘扇孔注意下对齐扇出:上述一致问题,优化下电感内部的挖空区域:个别信号没有联通:其他的没什么问题。

电感当前层的内部挖空处理:上述一致问题:注意不同地之间至少满足2MM间距:变压器信号除了差分信号,其他加粗20MIL走线:注意差分对内等长的GAP大于等于3W:焊盘扇孔注意对齐扇出:注意等长线之间满足3W间距原则可以调整下:注意的过孔之间的

单击一般工具栏中的布线图标,调出布线工具栏 从左到右依次为布线、扇出、优化、调整、居中。布线:布线指令会将所选取的对象进行交互式自动布线设计扇出:自动针对所选取的SMT元件、单个管脚或网络做扇出布线,并按照设定的规 则进行分析布线优化:

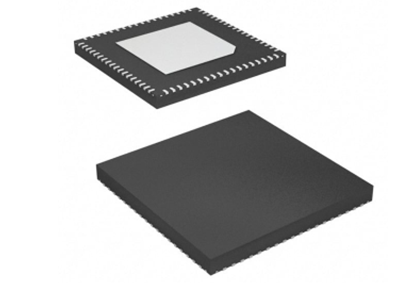

概述1、ADCLK846BCPZ 是一个1.2GHz LVDS/CMOS,扇出缓冲区优化的低抖动和低功耗操作。可能的配置范围从6 LVDS到12 CMOS输出,包括LVDS和CMOS输出的组合。两条控制线用于确定输出的固定块是LVDS还是

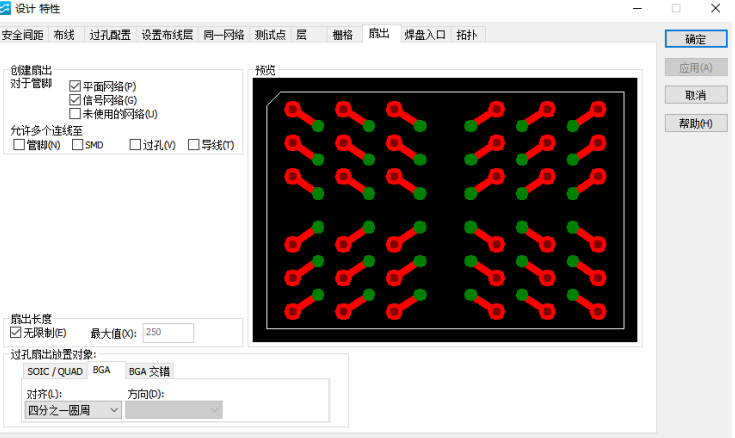

BGA扇出介绍

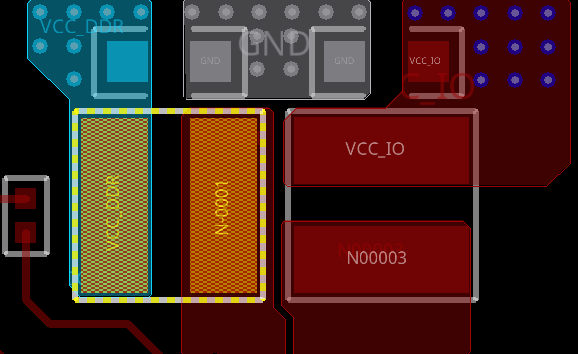

BGA扇出前须设置好规则,将BGA下方器件挪走,BGA下方所有层布线清除,若扇出时有DRC产生,会导致扇出失败。扇出前将格点设置为PIN间距的一半或者0,设置为PIN间距一半时须将精度设置好,否则会导到设置的格点4舍5入,设置失败。选择好合

答:我们PCB布局完成之后,需要对网络进行扇出,一般空的管脚、空的网络不需要进行扇出,为了提高布线效率,我们会对空的网络进行高亮显示,具体的操作步骤如下所示:

全站最新内容推荐

- 1常规变压器耦合型自激调频式开关电源电路分析讲解

- 2低压MOS在多电平逆变器上的应用-REASUNOS瑞森半导体

- 3走进电子元件,了解双稳态触发器

- 4模拟电路太难读?有没有可能是你不会看!

- 5要使用电烙铁,应该注意什么?

- 6硬件设计:4.10 通过这个实验,你会深刻认识到电感滤波与电容滤波电路的区别(为什么电容型滤波电路不能用在大电流环境)

- 7硬件设计:4.8-4.9 电感教程_滤波电路_低通滤波电路为什么分为电容型和电感型

- 8硬件设计:4.7电感教程_为什么有些开关电源在上电时会过压_怎么解决

- 9硬件设计:4.6 电感教程_5V电压升至1万V电压的工作原理

- 10硬件设计:4.5 电感教程之开关电源教程(boost型)_重新认识电感的重要性

扫码关注

扫码关注