- 全部

- 默认排序

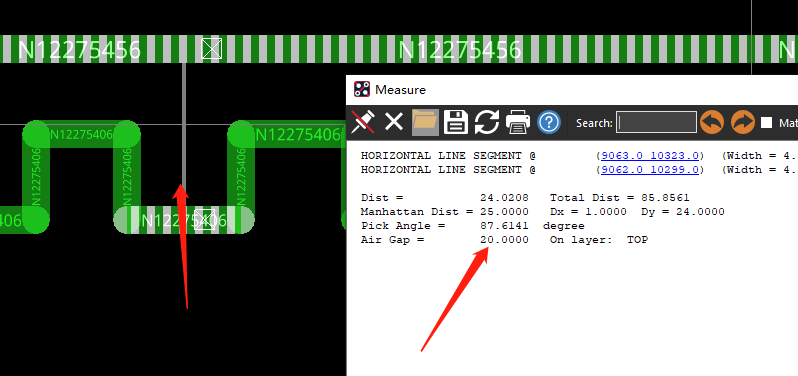

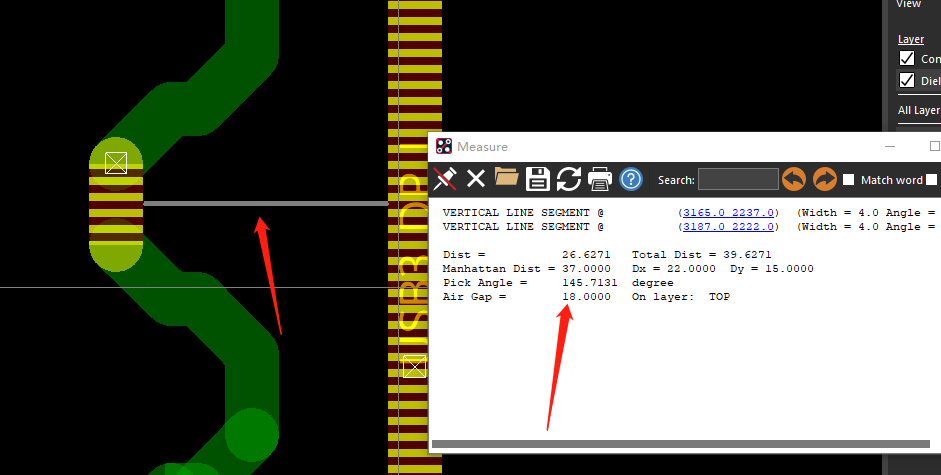

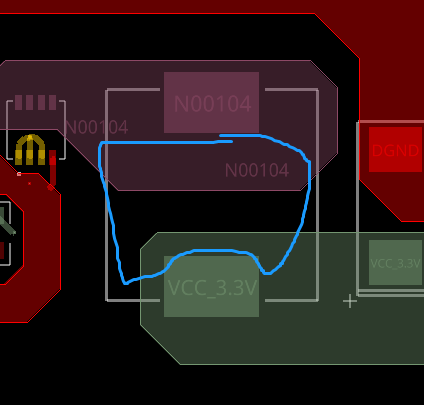

差分对内等长凸起高度不能超过线距的两倍2.蛇形等长尽量用45度,不要用直角,后期自己优化一下3.差分走线可以在优化一下4.差分出线要尽量耦合,后期自己优化一下5.注意确认一下此处走线是否满足载流注意器件摆放尽量电容靠近管脚存在开路差分对内等

要求单点接地,一路dcdc的地网络焊盘都连接到芯片下方打孔,顶层不要整版铺铜器件尽量中心对齐,相邻器件类似封装不要一个横着一个竖着,尽量朝同一方向布局相邻电路大电感朝不同方向布局反馈信号走线避开干扰源,不要走到电感下方以上评审报告来源于凡亿

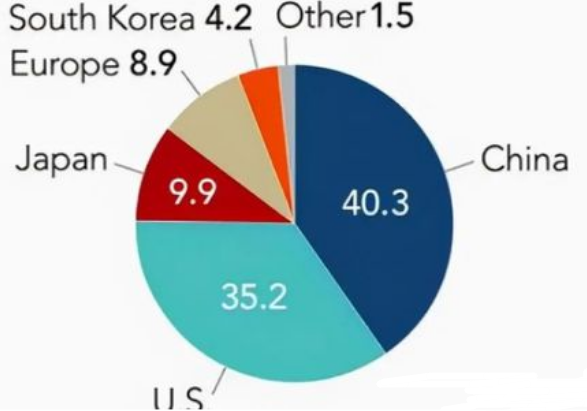

今年3月份,以台积电、高通、Intel等为首的行业巨头联合创立Ucle产业联盟,并推出全新的通用芯片互连标准——Ucle,旨在共同打造Chiplet互连标准。成为企业钟爱的电子工程师,选择凡亿教育《弟子计划:高速PCB设计&1对1》同一时间

注意差分对内等长凸起高度不鞥超过线距的两倍2.差分出线要注意耦合3.一层连通无需打孔4.注意器件不要干涉5.注意走线不要走到焊盘上面

电源管脚拉出来之后加粗到15MIL:HDMI差分组 组内等长以及组跟组等长误差没问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.co

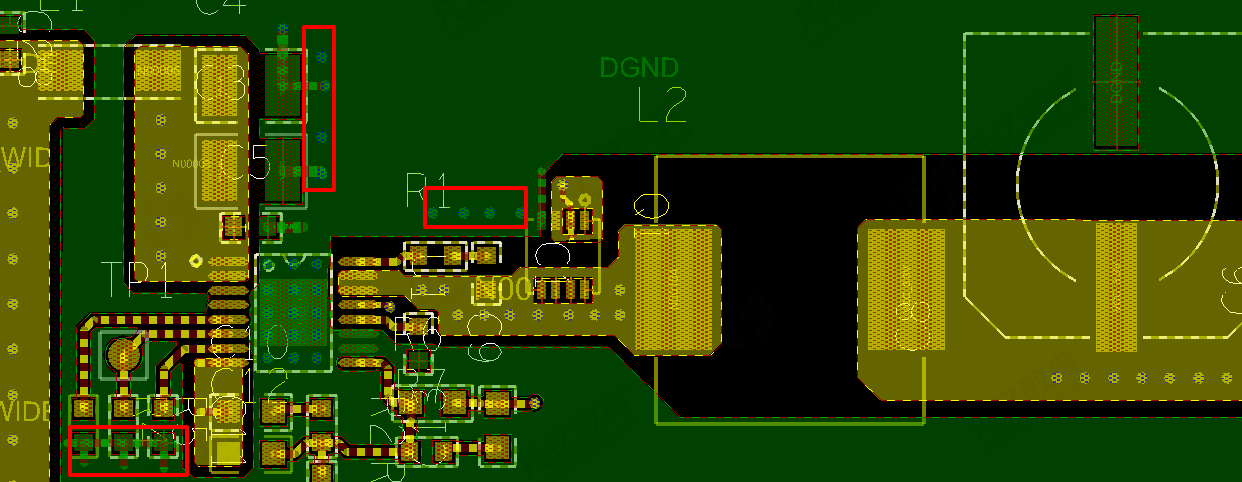

注意差分凸起高度不能超过线距的两倍2.差分走线需要优化一下3.时钟信号尽量包地处理4.电容尽量靠近管脚均匀摆放5.差分出线要尽量耦合,后期自己优化一下6.存在多处开路后期自己在顶底层铺上电源和地铜皮7.变压器需要挖空所有层处理

据外媒报道,今年年初,美国和日本合作制定5G标准后,正佳加快速度推进这一计划,争取在2024年共同推出6G标准,这项行为或将促使中国和欧洲再度合作制定6G标准。欲成射频工程师,来凡亿教育!活动特惠!满300-30!《弟子计划:毫米波天线阵列

我是2018年09月18号加入凡亿弟子计划跟着郑老师学习AD画板子的。郑老师在和我通过电话,了解了基本情况以后,制定了学习计划。从最基本的电源模块入手开始学习如何画板,通过这两个月的学习,现在已经能把SDRAM画好了,这里说说这两个月来的感受。

注意电感所在层的内部需要挖空处理2.注意滤波电容摆放应该先大后小摆放3.开关电源电感下面应该避免走线4.芯片采用单点接地,其他部分应该避免打孔,只需要在芯片中间打孔即可5.后期需要在底层铺整版地铜

Python标准库有超过200个模块,大部分工程师经常在程序中导入和使用,但总有部分好用的模块仍然没被注意到、今天凡亿教育为小伙伴们搜集了五个你可能不知道但很好用的Python模块。零基础小白如何成为Python工程师?来《弟子计划:Pyt

扫码关注

扫码关注