- 全部

- 默认排序

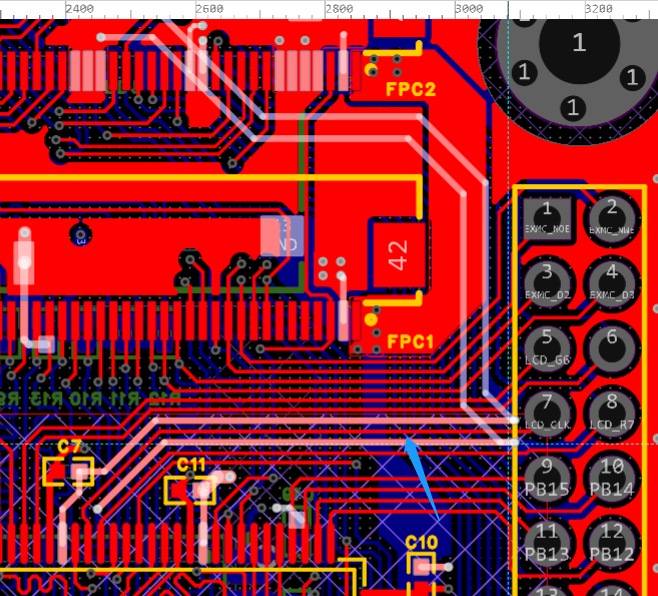

时钟信号包地需要在地线上间隔150mil-200mil打上一个地过孔2.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.器件摆放注意对齐处理4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊;地网络打一个孔即可,

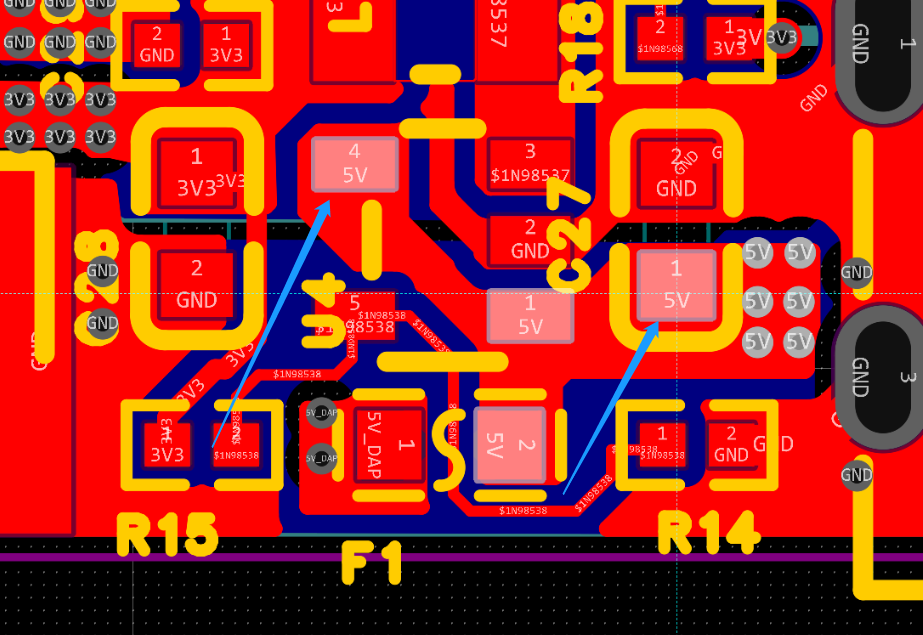

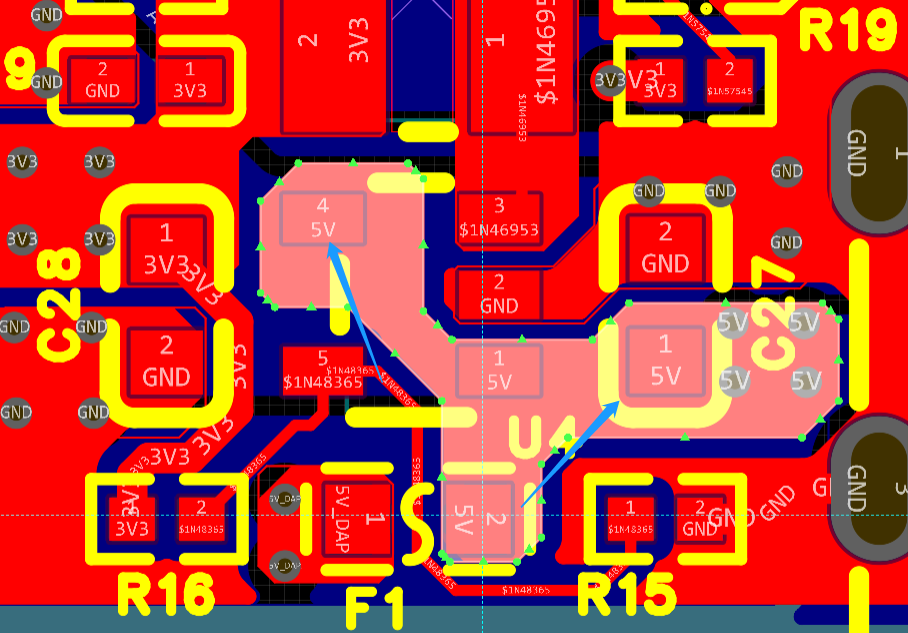

电源输入的滤波电容应该靠近输入管脚(4脚)放置2.此处走线需要优化一下,尽量不要有直角,走线不要从器件中间穿3.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍4.器件摆放注意局部对齐处理5.logo图片最好不要放在焊盘上【问题改善建

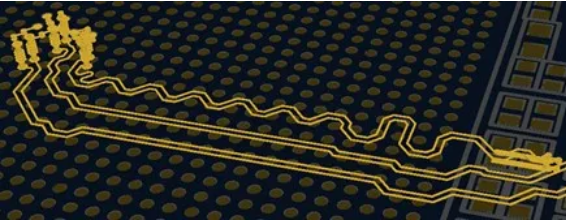

答:我们在进行PCB设计的时候,对于差分信号换层,都是双击进行打孔,但是双击打孔的间距是系统默认的,有时候会导致过孔间距太近,影响信号的质量,如图6-283所示,我们是否可以手动去控制差分过孔之间的间距呢,当让是可以的,我们这里讲解一下具体的处理方法,如下所示:

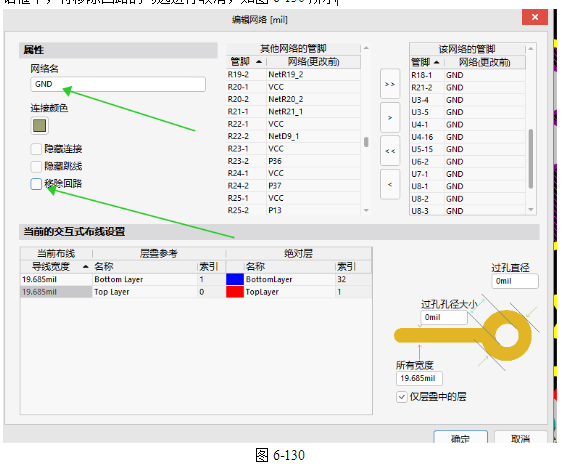

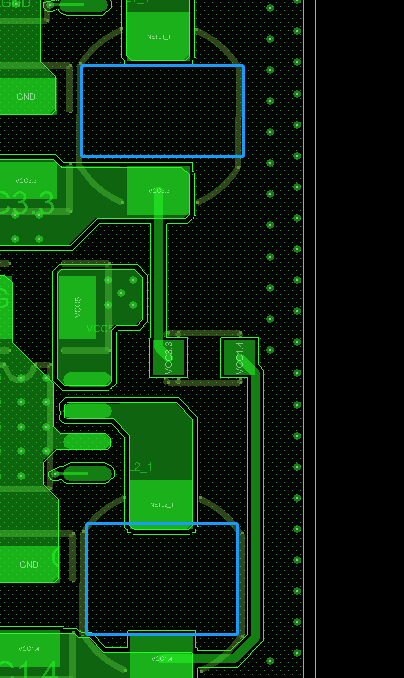

在pcb设计中由于不允许出现回路,因此会对网络进行自动移除回路的设置。然而在地线中因为要对某些信号线或差分线进行立体包地,所以会对地线单独设置不自动移除回路

在高速PCB设计中,差分信号的应用越来越广泛,这主要是因为和普通的单端信号走线相比,差分信号具有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。作为一名(准)PCB设计工程师,我们当然需要充分理解差分信号!

电感所在层测内部需要挖空处理2.地分割间距最少控制1mm以上,有跨接器件的地方不满足可以忽略,其他地方尽量一致3.除差分线外,其他的都需要加粗到20mil4.注意过孔尽量不要上焊盘5.注意等长线之间需要满足3W6.地址线也需要添加等长组进行

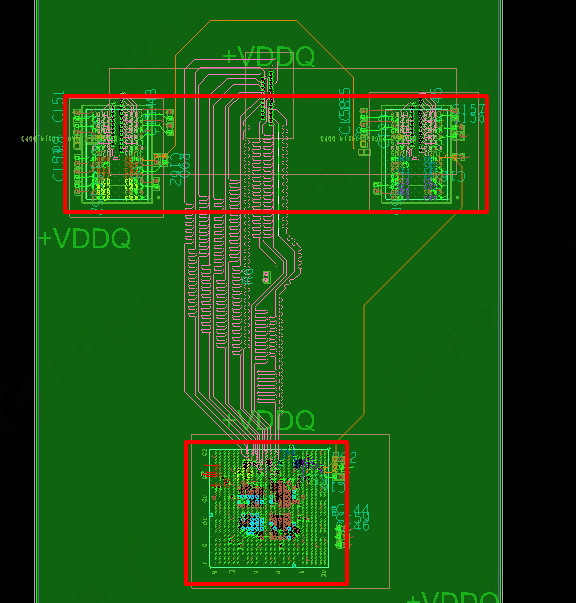

ddr之间ddr和芯片距离太远,ddr到芯片推荐600-800mil器件摆放太近丝印干涉,滤波电容推荐摆放到ddr背面靠近焊盘放置 过孔上焊盘,小器件焊盘尽量不要打孔到焊盘上差分线是主要时钟信号,尽量缩短走线电容靠近ddr中间放置差分线等长

1.电源输入的滤波电容应该靠近输入管脚(4脚)放置2.走线尽量不要从器件中间穿,自己调整一下走线路劲3.此处出线载流瓶颈,载流计算都是以铜皮在窄处进行计算4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍5.器件摆放尽量对齐处理6.

扫码关注

扫码关注