- 全部

- 默认排序

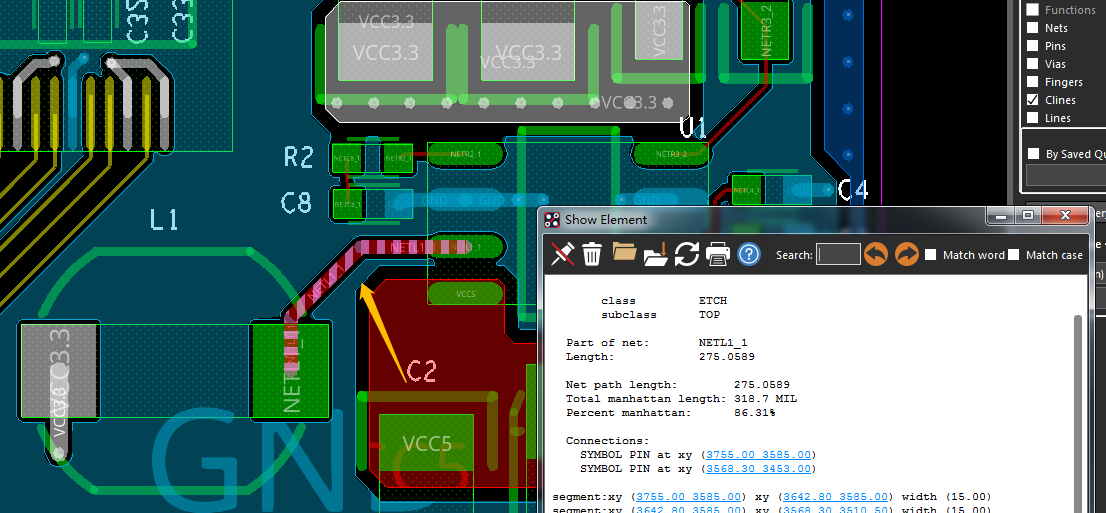

电源信号建议铺铜处理:注意电源模块的布局。输入输出都是铺铜处理:电感底部不要走线:上述一致原因:建议看下自己的电源模块设计需要优化。晶振前面的滤波电容位置是否反了 走线是要π型滤波 gnd管脚放置外部来将晶振进行包地处理:上述一致问题:等长

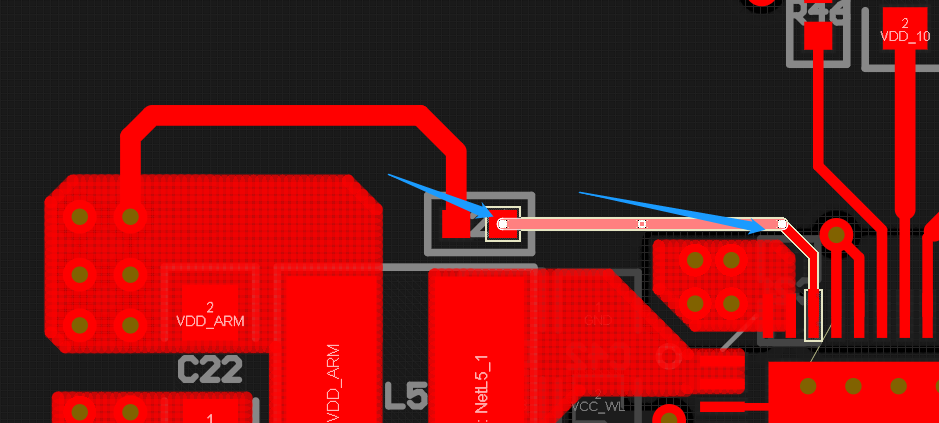

差分建议包地 已经打了地过孔直接拉线包上就行了:回流地过孔打在差分打孔换层的两侧:注意此处的扇孔,不要吧内层平面割裂了:差分等长GAP需要大于等于3W:注意差分等长误差:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB

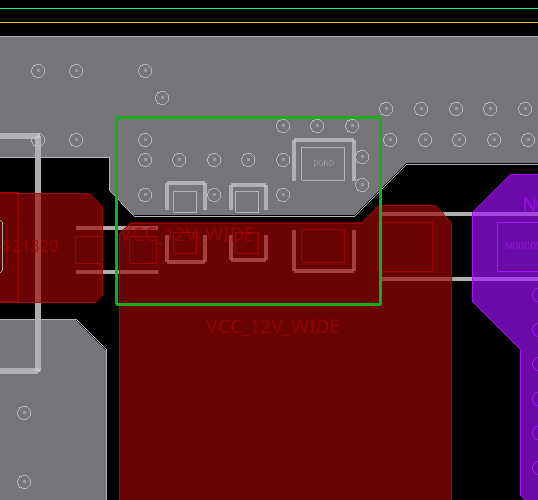

看下原理图此处三个电容位置是否有问题:看下哪个电容才是输入主干道上的电容,重新理解清楚再去放置。输入主干道上的电容是先大后小,放置有问题,自己去修改:电感当前层内部注意挖空:注意主干道电源不要打那么多孔,如果是输入就打第一个输入口;如果是输

今天我们一起来了解下我们平时在PCB设计当中铺铜以及完成之后整版地铜皮的处理要点,我们一般我们在画完PCB之后都会在我们的PCB的外层和内层大面积的覆铜,这好像是一个共识,但是呢!其实这个覆铜也不能乱铺的,我们要针对不同的产品做不同的处理。

器件靠近管脚放置,反馈线宽尽量一致 ,10mil即可2.电感所在层的内部需要挖空处理3.注意过孔不要离焊盘太近4.相同网络的走线,焊盘和铜皮没有连接在一起,后期自己更改一下铜皮属性5.存在开路6.打孔尽量对齐7.反馈需要走10mil以上以上

随着信息技术和微电子技术的高速发展,新兴技术层出不穷,人工智能、新能源、物联网、大数据等已开始成为科技行业当下的新风口,尤其是在华为鸿蒙系统和“万物互联”新概念的提出,物联网逐渐大火。近日,无锡首届移动物联网大会(2022)如期举行,本次大

生成式AI是指使用AI和机器学习算法使机器能够创建新的数字视频、图像、文本、音频或代码的技术。生成式AI由算法驱动,这些算法具有识别输入的底层模式、生成类似输出并提供高质量内容的潜力。一种更升级的生成式AI不仅仅是监视现实生活环境来生成内容

1. 成本Cost:任何一个卖硬件产品的公司的主要盈利一般来说就是销售价格-COGS,而COGS90%取决于设计,剩下就是生产成本了,这个价格一般来说比较透明,代工厂 也很多,竞争激烈。虽然说设计成本60%也取决于主要芯片的价格(这个主要要靠公司高层跟芯片厂商谈判的结果了,HW的作用有限,更多是系统工程师做决策 用什么芯片能符合产品需求和软件功能需求),但是剩下的电阻,电容,电感,二极管,三极管

PCB设计中,对于静电的防护,一般采用隔离、增强单板静电免疫力和采用保护电路三项措施来进行电路设计。 深圳pcb设计培训班对于PCB上的静电敏感元器件,在布局时要考虑其布局在远离干扰的地方,特别是离静电放电源越远越好,还有就是电气隔离,金属外壳; 增强免疫能力,在面积允许的情况下,可以在PCB板周围设计接地防护环,可以参考CompactPCI规范。大面积地层、电源层,对于信号层,一定要紧靠电源或者地层,保证信号回路最短,对于干扰源高频电路等,可以局部屏蔽或者单板整体屏蔽,在电源、地脚附近加不

扫码关注

扫码关注