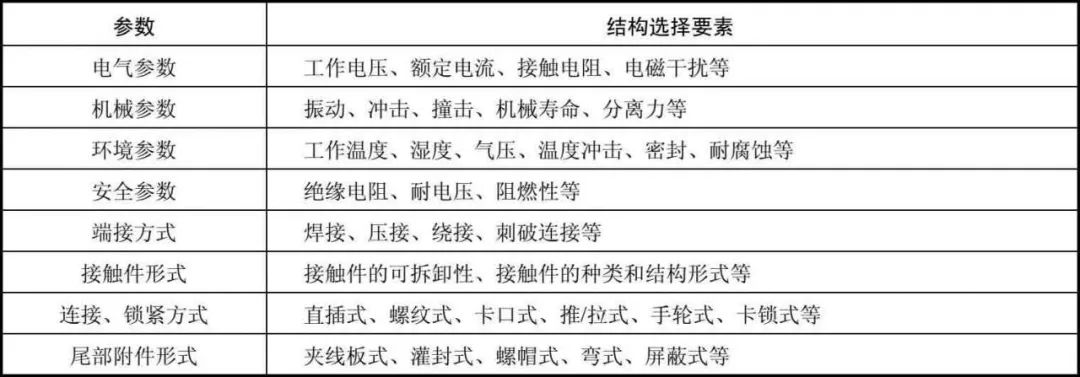

今天我们一起来了解下我们平时在PCB设计当中铺铜以及完成之后整版地铜皮的处理要点,我们一般我们在画完PCB之后都会在我们的PCB的外层和内层大面积的覆铜,这好像是一个共识,但是呢!其实这个覆铜也不能乱铺的,我们要针对不同的产品做不同的处理。我们下面也也列举了几种不同类型的PCB的处理方法

首先电源类PCB通常电流都比较大,电压呢也非常的高,通常我们在处理高压的PCB的时候都不会铺铜,因为如果存在高压就必须要考虑的一点就是爬电间距,高压与低压之间的爬电间距太小的话会有安全隐患,通常电源板子里面很多网络都要设置不同的安全间距,如果到时候我们铺整版铜皮的话大部分也都是碎铜,我们一般的PCB大面积的铺铜是会有屏蔽的作用,但是像一般的电源PCB板子没有必要这样做,碎铜不仅没有屏蔽的效果,反而会影响我们的信号。

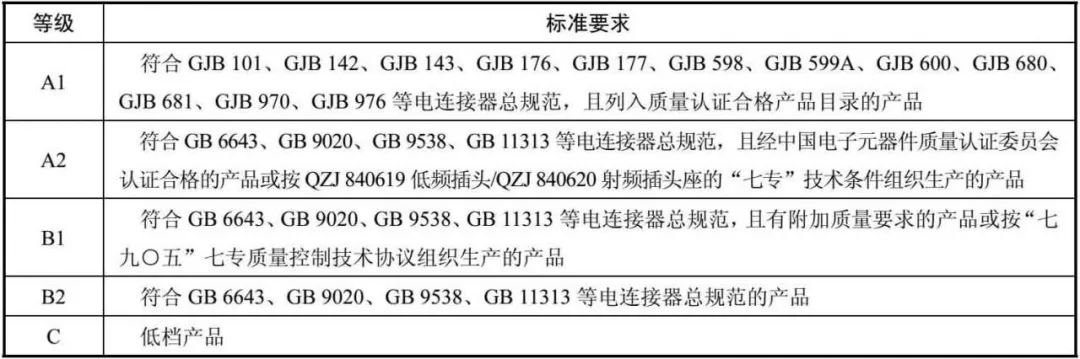

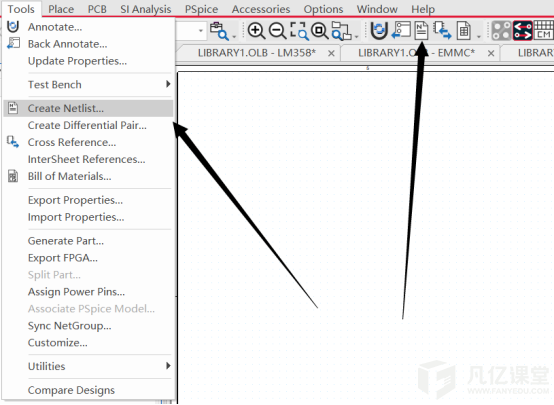

接着就是高速PCB的设计当中我们铺整版铜皮的时候,我们也是需要注意的,一般我们的铜皮和需要控阻抗的信号线需要保持一定的距离,不然也会影响到信号的阻抗,我们应该如何理解我上面所说的呢?我们可以做一个验证。

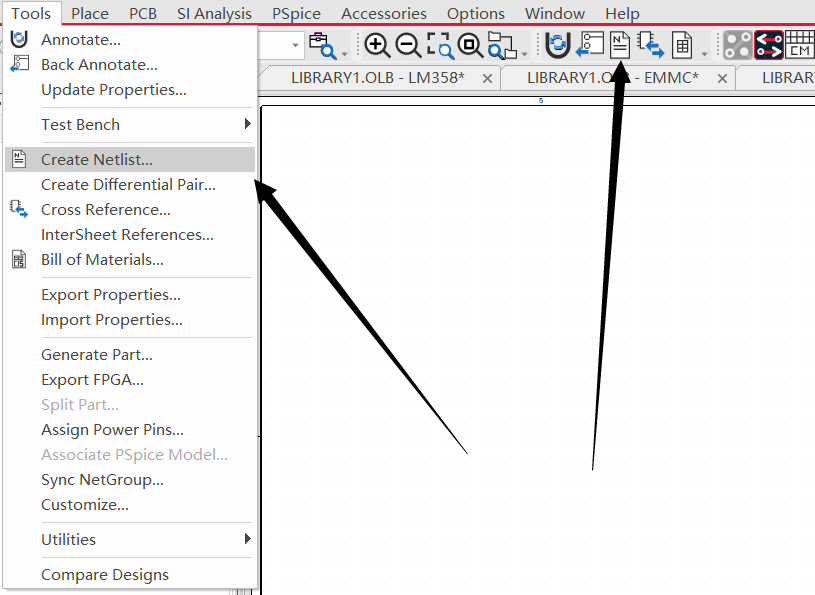

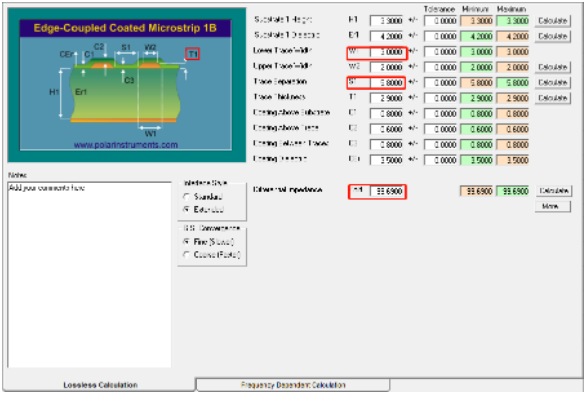

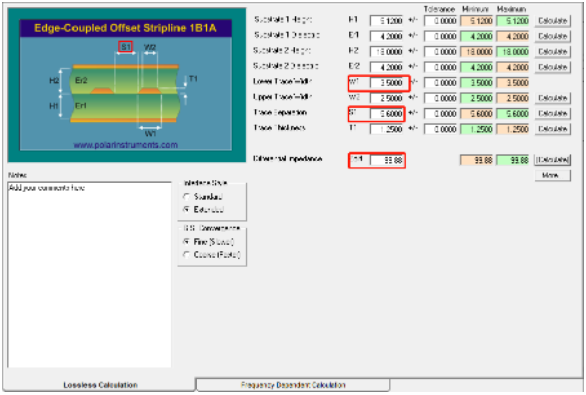

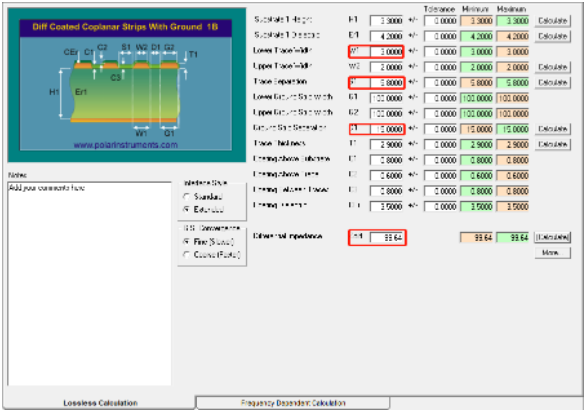

我们用以上叠层来看看铜皮对阻抗的影响,我们先算一下表层100om差分和内层100om差分的线宽线距是多少。

我们可以看到上面的外层和内层100OM线宽线距分别是3mil/5.8mil(表层)和3.5mil/5.6mil(内层),那么这个时候我们再算一下假设我们的差分线两侧有铜皮的情况下会对我们的阻抗有什么影响,其实就是我们平时说的共面参考。

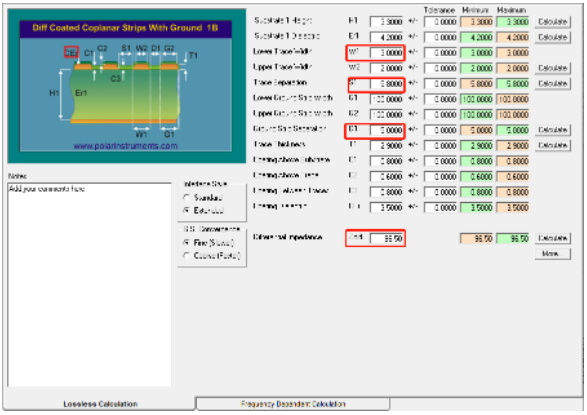

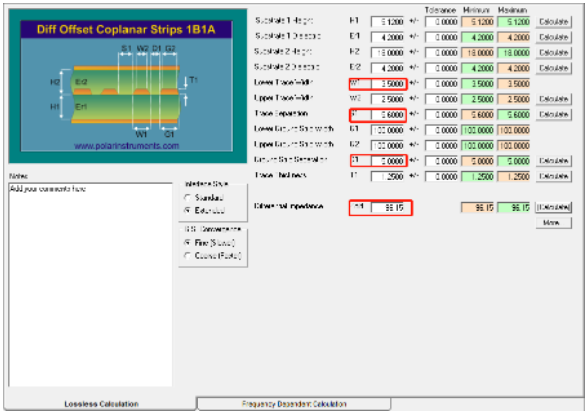

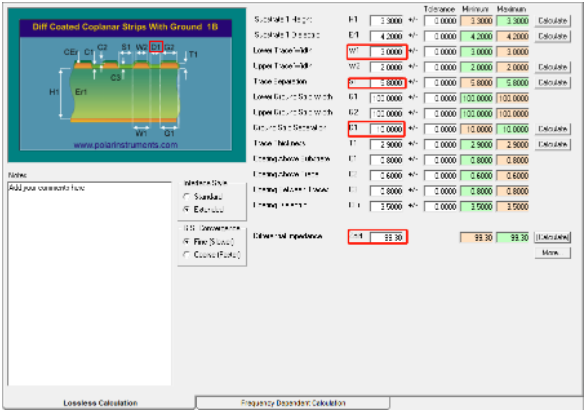

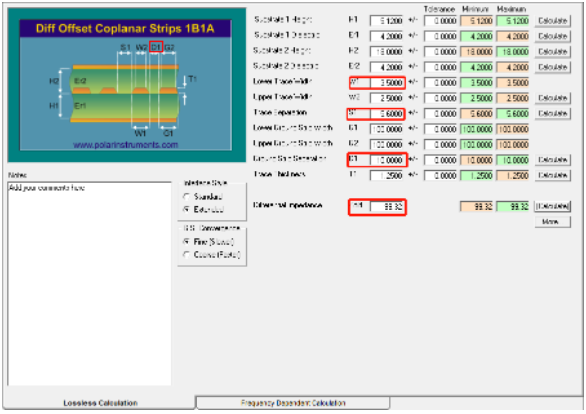

我们可以看到还是外层和内层假设我们差分两侧是有铜皮的情况下,而且铜皮离差分线5mil的间距,这个时候不管是内层还是外层的差分阻抗都会大概下降3om,所以我可以得出铜皮离我们的阻抗线太近的情况下会使得阻抗降低,所以我们在设计高速PCB的时候我们在铺整版铜皮的时候,一定要注意间距问题,我们要给阻抗线设置个铜皮间距规则,那么问题又来了,我们应该设置多少的间距呢,那么这个问题我们继续验证一下,我们看看铜皮离差分线10mil以及15mil的时候我们的阻抗会有多大的变化。

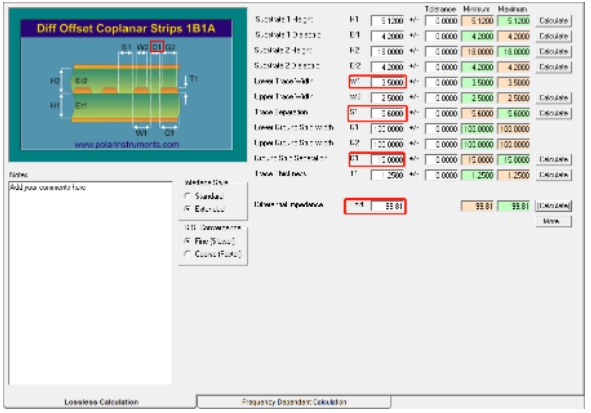

我们根据我们的计算可以看得出,铜皮离差分线越远对阻抗影响越小,在安全间距为10mil的时候大概还是下降了0.5om的样子,但是比离5mil间距的时候好多了,如何在15mil的时候对我们阻抗的影响几乎可以忽略不记,所以我们可以更具上面这些信息得出我们设置安全间距的时候尽量要大于15mil,这样同层的铜皮对阻抗的影响才比较小,如果我们还用空间的情况下设20mil间距就更好了,所以我们铺铜的时候一定要注意铜皮与阻抗线的间距,我们也不建议大家直接铺整版铜皮,一般推荐大家通过铺小铜皮的方式把空余的区域补全,这样子是最好的,也不会出现一些碎铜,然后也可以时刻关注铜皮与阻抗线的间距!

声明:本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注