- 全部

- 默认排序

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到八层板的叠层来进行示例讲解单面PCB板和双面PCB板的叠层对于两层

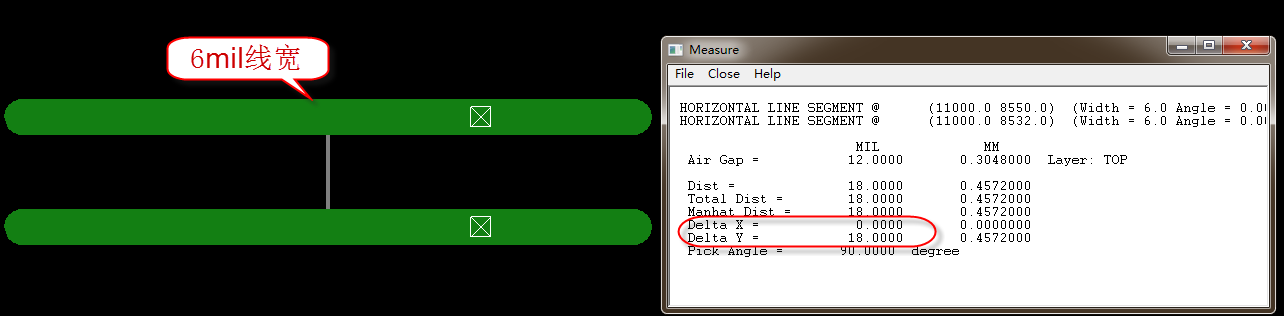

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在Allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

提到6层板分层布局,一般业内主流会推荐这个设计方案:【电源层数1,地层数2,信号层数3】但从成本方面考虑,我们会希望板子布局越多线路越经济,即信号层越多成本越低。因此,在设计6层板时,电源层和接地层均只布局一层,信号层设计4层,理论上是比较

答:正片,一般是pattern制程,其使用的药液为碱性蚀刻。是在顶层和地层的的走线方法,用Polygon Pour进行大块敷铜填充。其工艺为:需要保留的线路或铜面是黑色或棕色的,而不要部份则为透明的。经过线路制程曝光后,透明部份因干膜阻剂受光照而起化学作用硬化。显影制程会把没有硬化的干膜冲掉,然后在铜面上镀锡铅,然后去膜,接着用碱性药水蚀刻去除透明的那部分铜箔,剩下的黑色或棕色底片便是我们需要的线路。 负片,一般是tenting制程,其使用的药液为酸

在电子产品设计中,电磁干扰绝对是电子工程师最害怕的头号问题,为了有效控制EMI问题,工程师会采用多种方法,其中PCB分层堆叠设计是很有用的方法,下面将谈谈如何通过PCB分层堆叠来控制EMI问题。1、合理规划电源层与地层电源层应尽快乐能靠近地

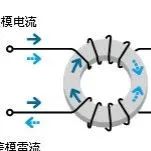

共模扼流线圈的原理

要理解共模扼流线圈,先要理解共模和差模的概念(一)共模和差模的概念通常,基板上电器电路中从某处流出的电流会通过符合到达别的电路,经由基板上的其他路线六回来。(很多时候返回路线为基板的接地层)这即为差模流动方式。图1 差模的传导路线另一方面,虽然不存在明确的架线,但却存在别的传导线路。因基板上的各配线

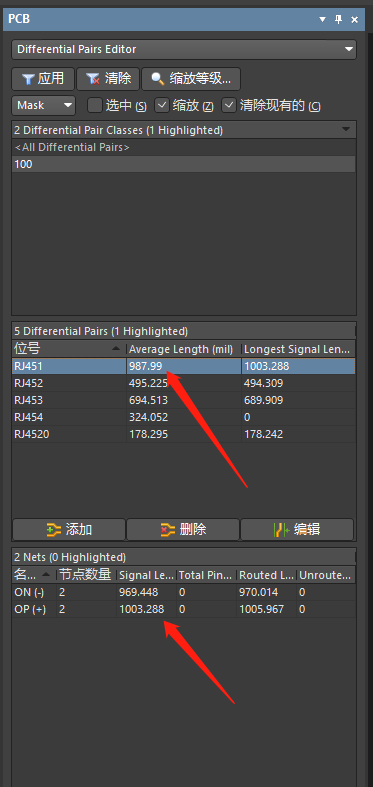

网口差分需要进行对内等长,误差5mil2.注意差分走线要注意耦合3.注意等长线之间需要满足3W规则4.等长存在误差报错5.地网络进行就近打孔,连接到地层,缩短回流路劲6.顶层BGA里面的铜尽量挖掉7.电感所在层内部需要挖空处理以上评审报告来

扫码关注

扫码关注