- 全部

- 默认排序

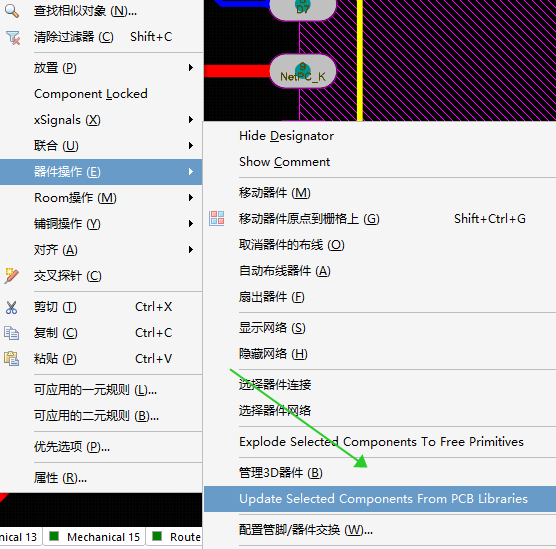

注意4层板不需要用埋盲孔2.反馈信号需要加粗到10mil,注意焊盘出线规范3.注意变压器负片层挖空处理,地分割注意规范4.注意丝印调整尽量不要干涉器件丝印以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

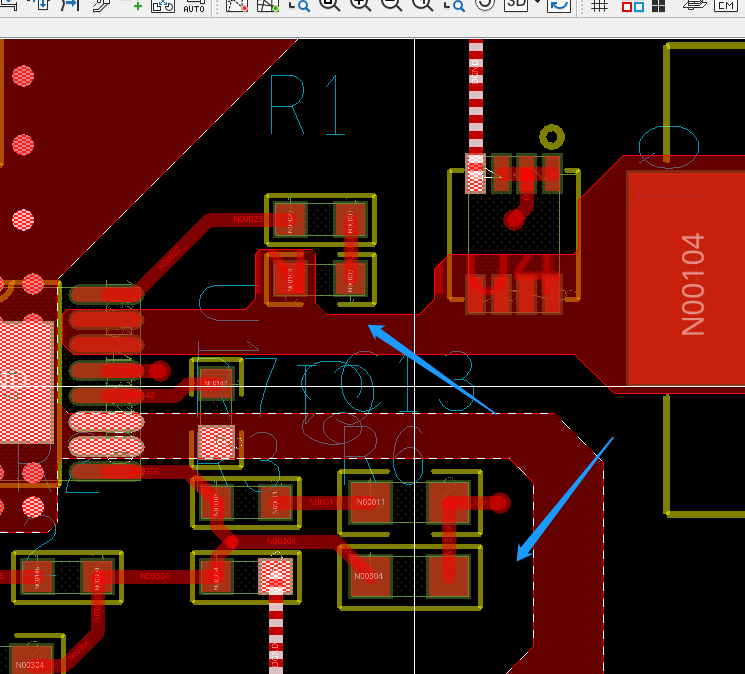

建议顶底层可以铺上大地铜:铜皮注意这种尖角:注意此处的铜皮 不要铺到晶振内部,晶振需要净空:晶振包地处理沿着器件丝印边框打孔:跨接器件两边可以多打地过孔:差分打孔换层的两侧可以放置地过孔,缩短回流路径:此处晶振净空调整下:等长之间注意保持3

配置电阻电容注意布局可以向下向上放置,中间腾出空间优先放置主干道上的器件:主干道上的器件布局优先级最高。建议吧静态铜皮转换为动态铜皮,设计基本放置动态铜皮:反馈信号走个8-12mil即可:注意器件丝印最好调整下,不要重叠了:注意同焊盘网络连

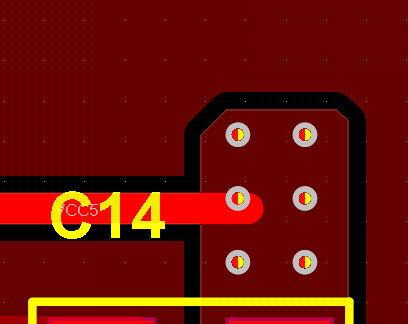

在出丝印文件时,怎么能三个元器件丝印和位号的颜色不一样让元器件丝印个位号颜色不一样让元器件丝印的颜色和对应位号的颜色不一样

扫码关注

扫码关注