- 全部

- 默认排序

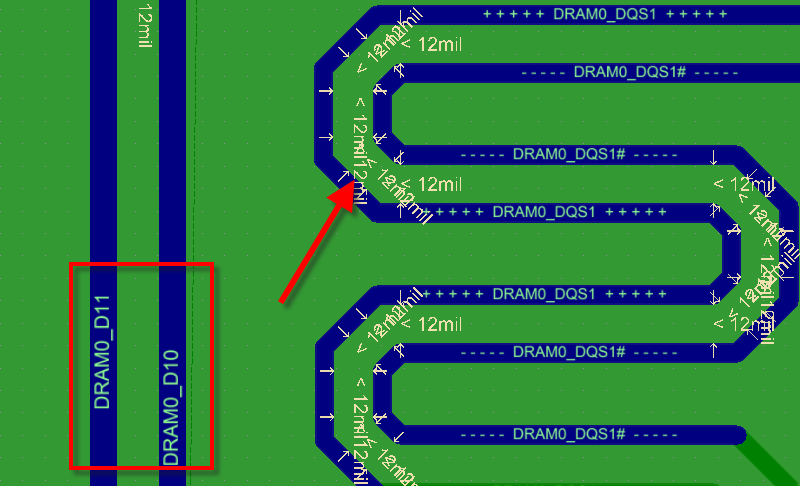

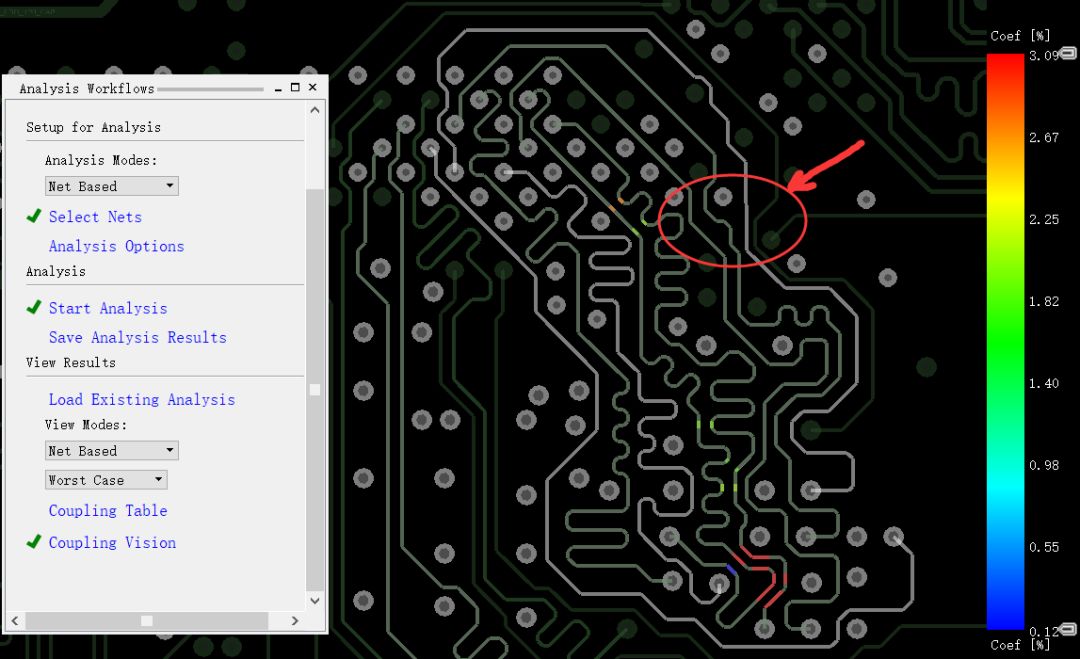

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

随着半导体集成度越来越高,PCB层间的串扰问题愈发严重,虽然很多电子工程师通过3W规则来解决串扰,但你知道吗?还有很多方法可以抑制PCB板的串扰问题。串扰CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

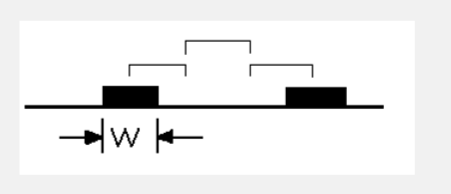

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。当我们的走线的中心间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则

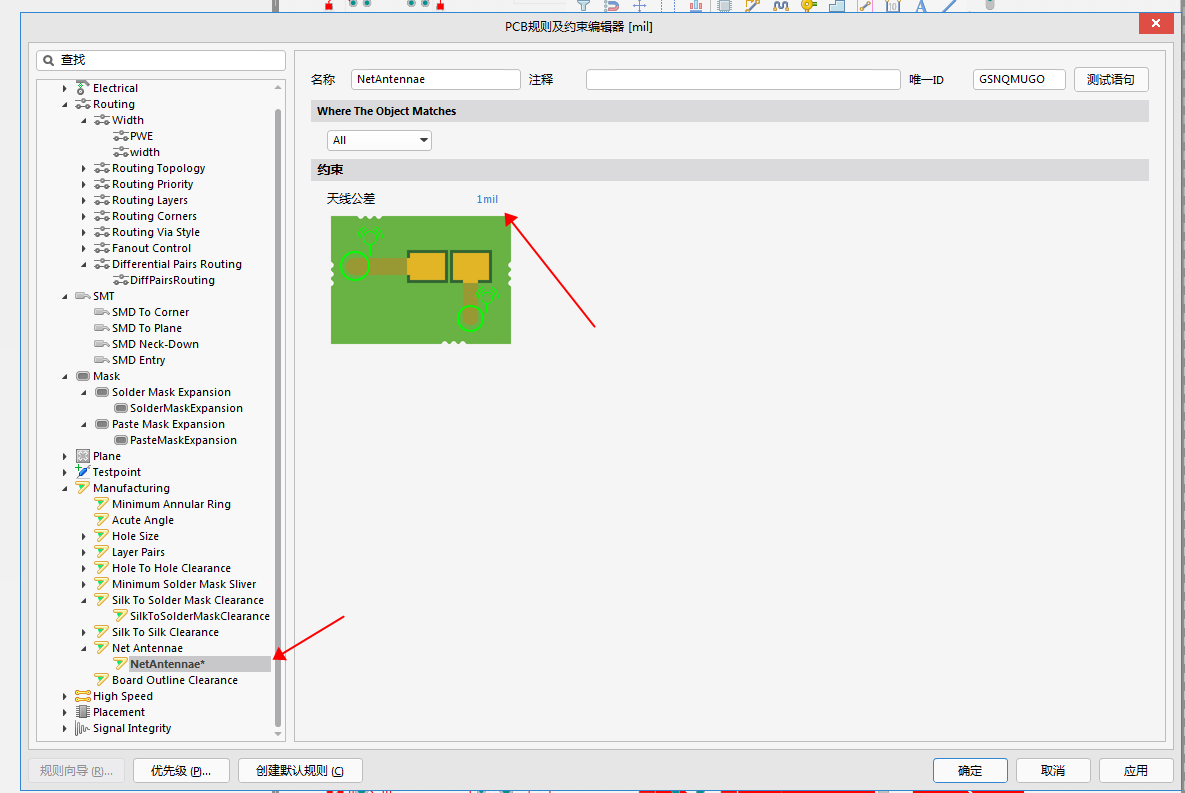

虽然可以对走线进行一些优化处理,但是考虑到还要人工进行布线处理,难免会对走线的一些线头有遗漏,这种线头简称Stub线头。Stub线头在信号传输过程中相当于一跟“天线”,不断地接受或发射电磁信号,特别是高速的时候,容易给走线导入串扰,所以有必要对Stub线头进行检查,并在设计中进行删除处理。

答:互感是引起串扰的两个重要因素之一,互感系数标志了一根驱动传输线通过磁场对另外一根传输线产生感应电流的程度。

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

我们平时在PCB布线的时候,对于比较重要的信号都要做特殊处理,比如包地或者时“3W”,所谓3w指的是线与线之间的间距要满足三倍的线宽,那么我们怎么理解这个3W原则呢,他是如何降低信号之间的串扰的呢?我们要了解这个原因可以先了解电容的概念,电

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

包地与串扰

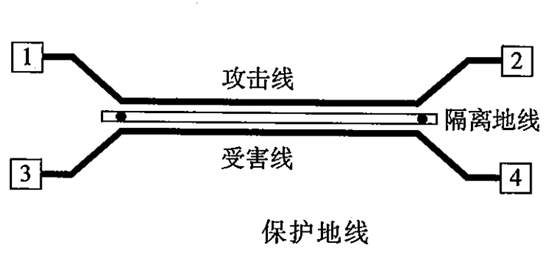

工程界常常使用保护地线进行隔离,来抑制信号间的相互干扰。的确,保护地线有时能够提高信号间的隔离度,但是保护地线并不是总是有效的,有时甚至反而会使干扰更加恶化。使用保护地线必须根据实际情况仔细分析,并认真处理。保护地线是指在两个信号线之间插入一根网络为GND的走线,用于将两个信号隔离开,地线两端打GN

扫码关注

扫码关注