- 全部

- 默认排序

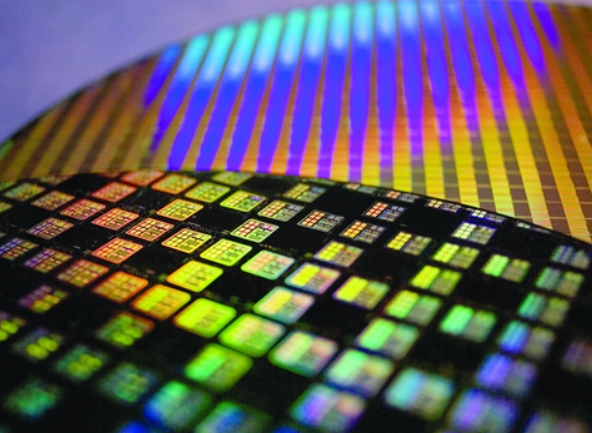

芯片设计,某种程度上越来越同质化。设计软件,无非是那两三家EDA公司,工艺,无非那几个晶圆厂。IP,例如cpu,主要是ARM core。用到的库,也基本上都是由晶圆厂推荐或者提供。如果是拼算法,拼生态,我们的竞争力和美西方还有一定的差距。目

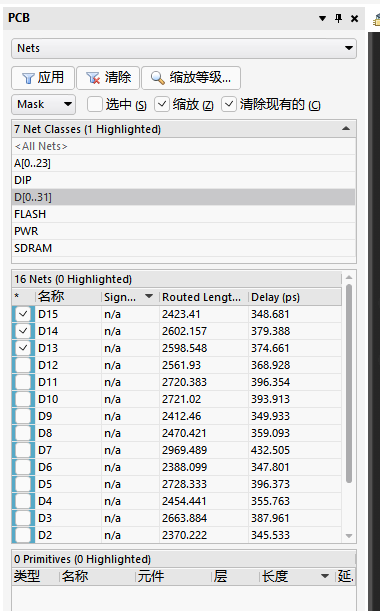

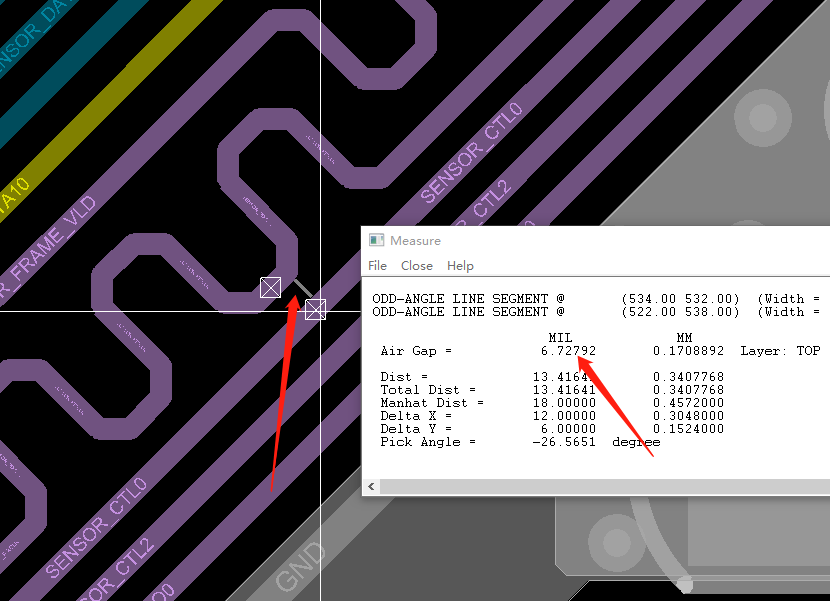

晶振需要走内差分处理2.SDRAM数据线低八位和高八位需要分开创建class,分别进行等长3.注意数据线之间等长需要满足3W规则4.地址线也需要满足3W规则5.滤波电容靠近管脚放置,尽量保证一个管脚一个6.数据线等长误差建议+-25,mil

众所周知,美国对华禁令,已经让多家厂商被迫裁减员工,退出中国市场,其中有三星电子、英伟达等,但这个队伍很快又增加一位。据国内媒体报道,在美国对先进人工智能(AI)芯片的出口管制下,AI芯片制造独角兽公司Graphcore宣布将裁减大部分中国

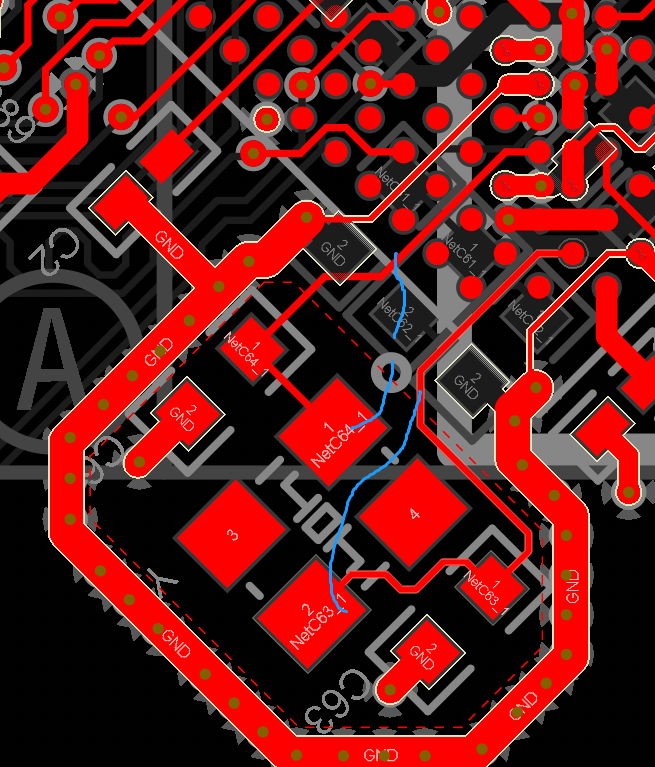

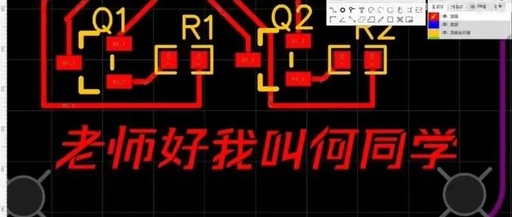

最近科技区顶流何同学,发布了新的视频,其中的PCB布局走线引起了讨论。我放了几张图,何同学的这张PCB有什么问题,欢迎大家留言!最后,分享下我整理的PCB设计的思维导图知识体系·PCB板材知识 PCB的组成和概念 PCB内部结构 铜箔 半固化片(PP) 芯板(core)·叠层 是什么 叠层设计的目的

数据线分组错误2.地址线分组错误3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.走菊花链的结构,等长应该是BGA到SDRAM,然后再从SDRAM到FLASH5.相邻焊盘是同网络的,不能直接相连,需要先连接焊盘之后在进

注意等长线需要满足3W规则2.此处铜皮可以在加宽一些,尽量加大载流能力3.电感所在炒年糕的内部需要挖空处理4.其他没什么问题以上评审报告来源于凡亿教育邮件公益作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ite

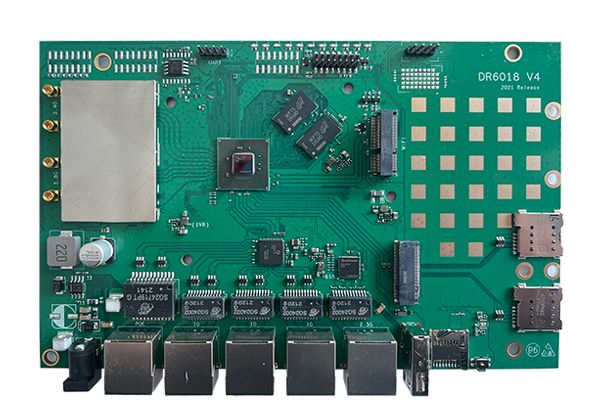

wallys--QCN9074 WiFi 6E Card OpenWRT, IPQ6010,802.11ax, 2x2 2.4G&5GQualcomm-AtherosIPQ6010Quad-core ARM 64bit A53 @1.8GH

扫码关注

扫码关注