- 全部

- 默认排序

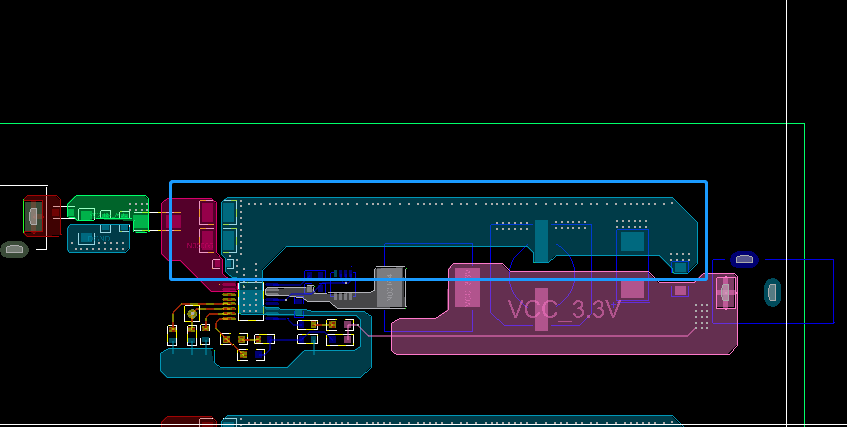

采用单点接地,此处不用打孔2.铜皮尽量不要有任意角度,一般钝角3.电感所在层的内部需要挖空4.反馈线尽量远离电感5.pcb上存在多处开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助

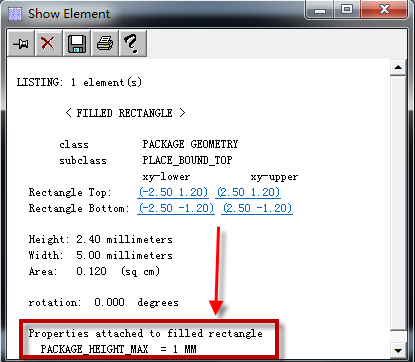

在做PCB设计时,有时结构上会对局部的器件布局有高度要求,不能将超过高度限制的器件放到限高区,否则会导致PCB装配问题。这个高度信息我们可以在做PCB封装时进行设置,设置好了就可以在设计时查看高度信息,辅助我们进行PCB设计。

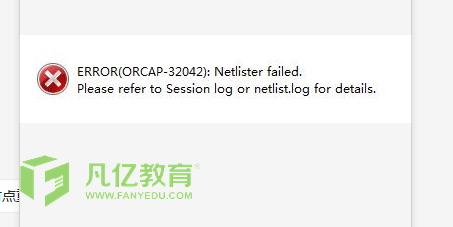

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”Netlister failed”的报错。

课程介绍:为了解决学员反馈的allegro操作难、新版本不会用、不知从何下手去学这个工具、不会安装等疑难杂症,我们本次课程采用了最新版本Cadenceallegro17.4来录制的。从原理图符号、原理图绘制、PCB封装、PCB绘制这几个方向

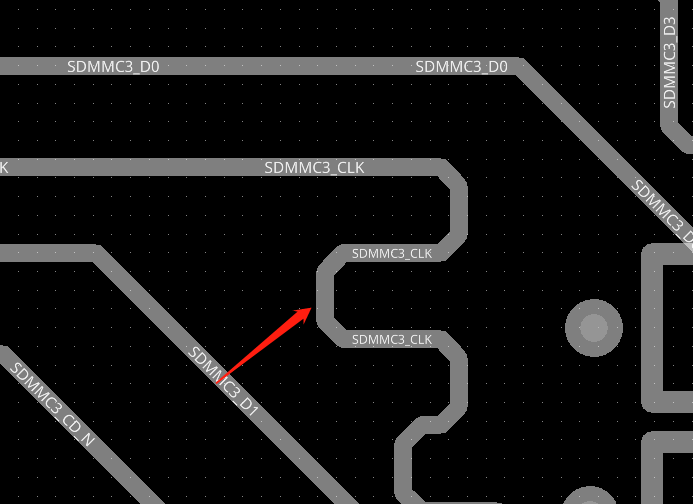

TF:注意数据线包地处理:SIM:数据线包地处理,用地线隔开:其他的没问题了 。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/it

扫码关注

扫码关注