- 全部

- 默认排序

主题;IC&SIP芯片封装设计与信号|电源完整性|电热仿真分析和建模1、IC&SIP产业封装设计验证工程师的前途集成电路IC&SIP设计处于集成电路产业的龙头地位,对产业整体的发展起着带动作用。未来几年内我国芯片生产有望每年以12%的速度递增,因此IC产业设计专业人才处于极度供不应求的状态。可以这样说,这正是我国很大程度上没有足够的IC产业设计人才的根源。

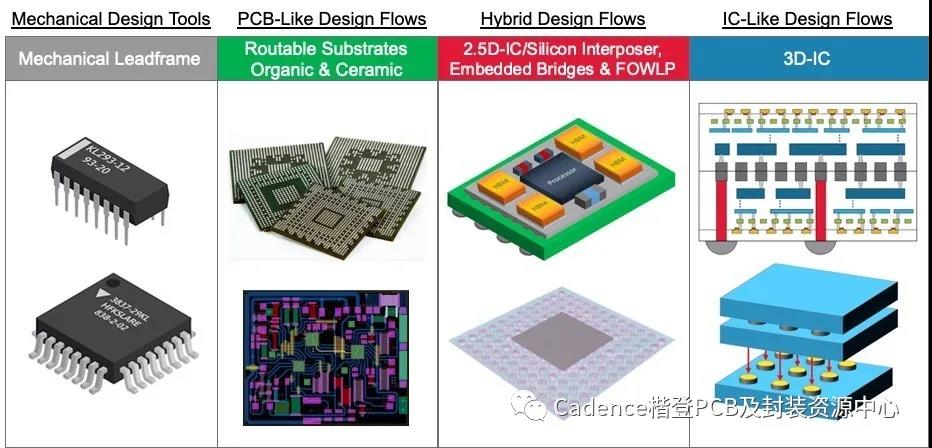

封装设计有许多处理方法: 采用以机械引线框设计封装本身 采用可布线的有机和陶瓷基板设计封装,这是一种PCB风格的设计流程 设计2.5D硅中介层、嵌入式桥和扇出型晶圆级封装(FOWLP)的混合设计流程 采用集成电路类设计流程设计具有硅穿孔(通常)的3D集成电路

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

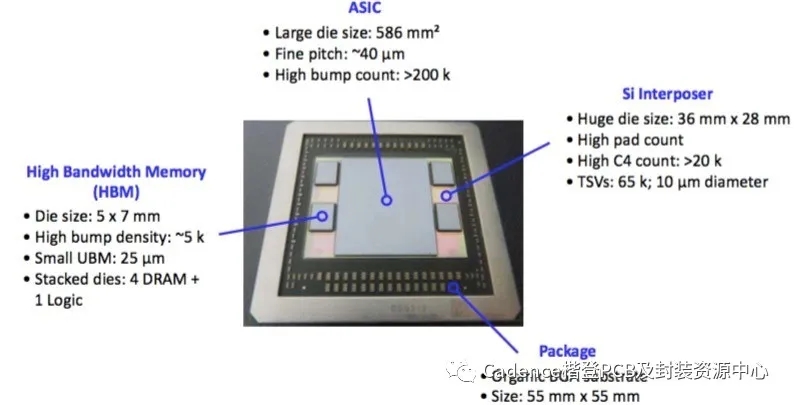

50多年来,半导体行业一直受益于摩尔定律。但是如今,半导体等比例缩小的时代已经结束。摩尔定律主要是作为一条经济法而存在——即集成电路上可容纳的晶体管数量,约每隔几年便会增加一倍。当然,是技术的发展使之成为现实;直到几年前,这一定律依然适用。高层次的经济主张是:每一代工艺将同一领域的晶体管数量增加一倍,成本仅增加15%,从而为每个晶体管节省35%的成本。但是因为当今的工艺愈发复杂,加之建造一个工厂的资本投入非常大(每台EUV步进机将耗资1亿美元),导致每一代晶体管都更加昂贵。因此我们发展出一个从7

扫码关注

扫码关注