- 全部

- 默认排序

我是2018年09月18号加入凡亿弟子计划跟着郑老师学习AD画板子的。郑老师在和我通过电话,了解了基本情况以后,制定了学习计划。从最基本的电源模块入手开始学习如何画板,通过这两个月的学习,现在已经能把SDRAM画好了,这里说说这两个月来的感受。

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø DDR, Dual Data Rate双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM,人们习惯称

DDR电路简介RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理电路16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。电路控制器有如下特点:1、兼容 LPDDR4/LPDDR4X/

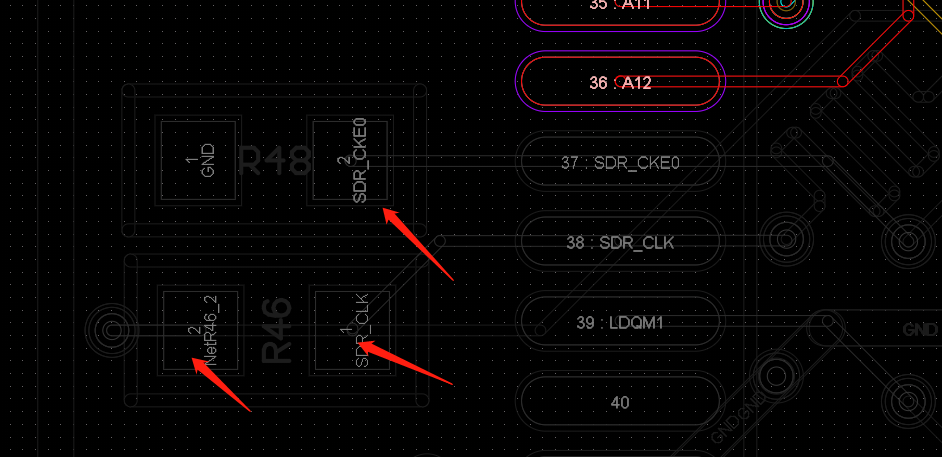

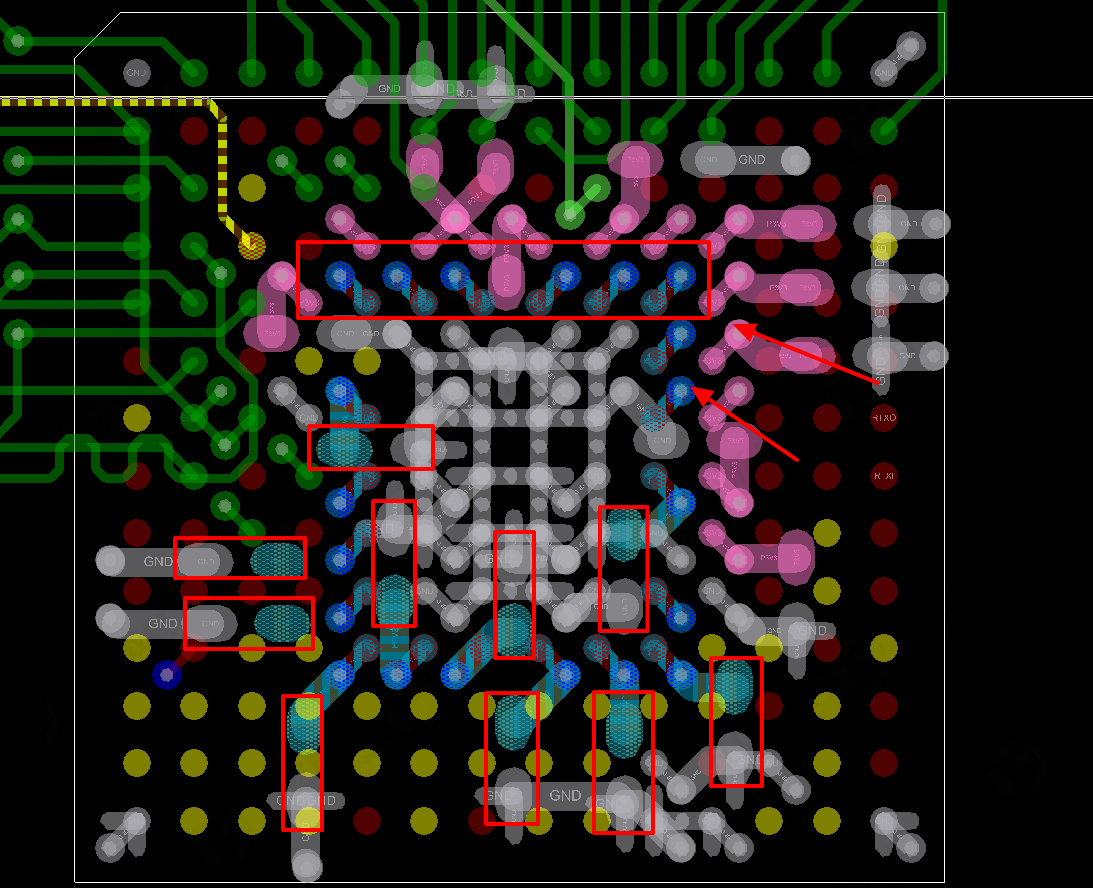

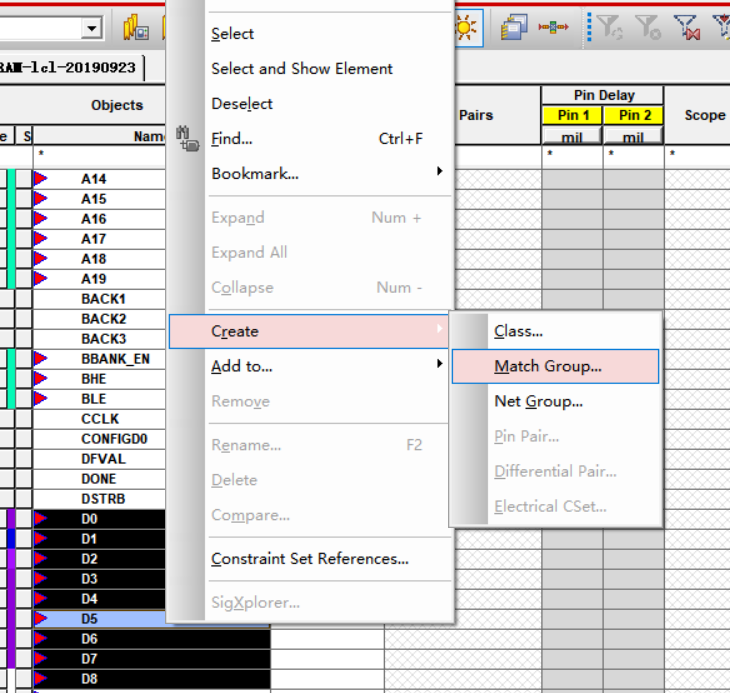

注意数据线等长需要满足3W规则2.地址线之间等长也需要满足3W规则3.注意数据线扇孔线宽尽量保持一致4.地址线等长存在误差报错5.等长组创建有问题,有很多网络没有添加到里面,后期自己重新创建一下6.注意走线不要有直角和尖角,尽量钝角7.注意

地址线分组,CLK,CKE0都要添加进来一起进行等长2.数据线分组应该是一组9根2SDRAM注意规则设置,导致等长有黄色提示2.注意过孔需要盖油处理其他没什么问题以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

1.芯片下方电容要均匀分布。2.数据线等长组分组错误,两组线分别缺少LDOM、HDQM。3.数据线等长错误,应该控制误差50mil4.地址线等长分组错误,缺少部分网络5.电源输入线宽不一致,电容输入输出都需要加宽。6.多存在多处尖岬铜皮。7

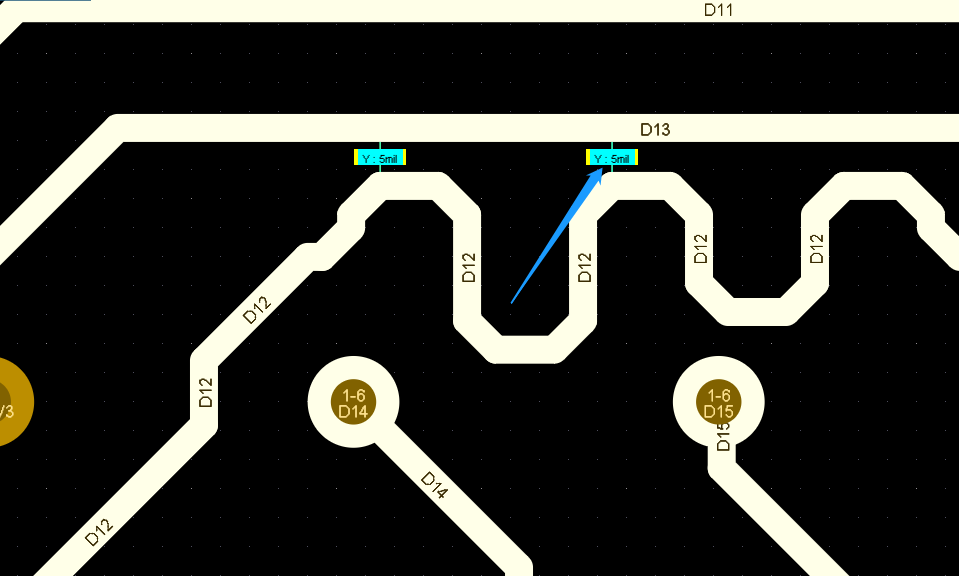

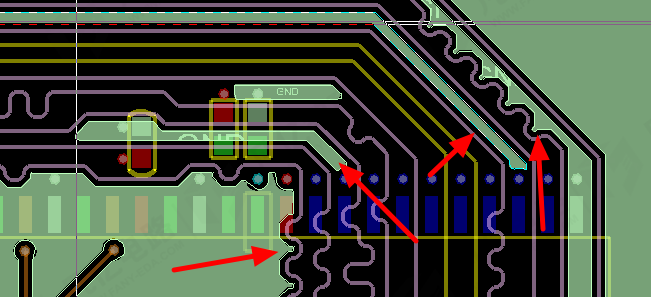

SDRAM信号线等长处理

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

存在多处尖岬铜皮和孤岛铜。2. 多处器件摆放干涉,如生产会造成两个器件重叠无法焊接。3.部分管脚存在开路。4.数据线分组错误,少了LDQM和HDQM5.地址线分组错误,缺少部分信号;以设计规范为准。以上评审报告来源于凡亿教育90天高速PCB

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

扫码关注

扫码关注