- 全部

- 默认排序

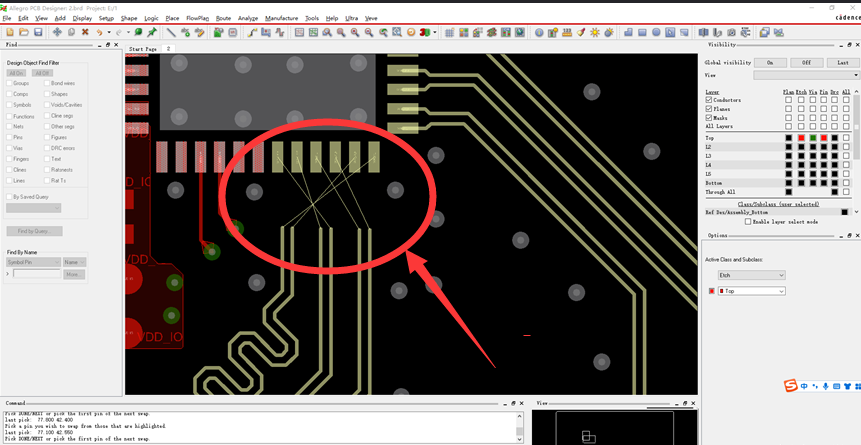

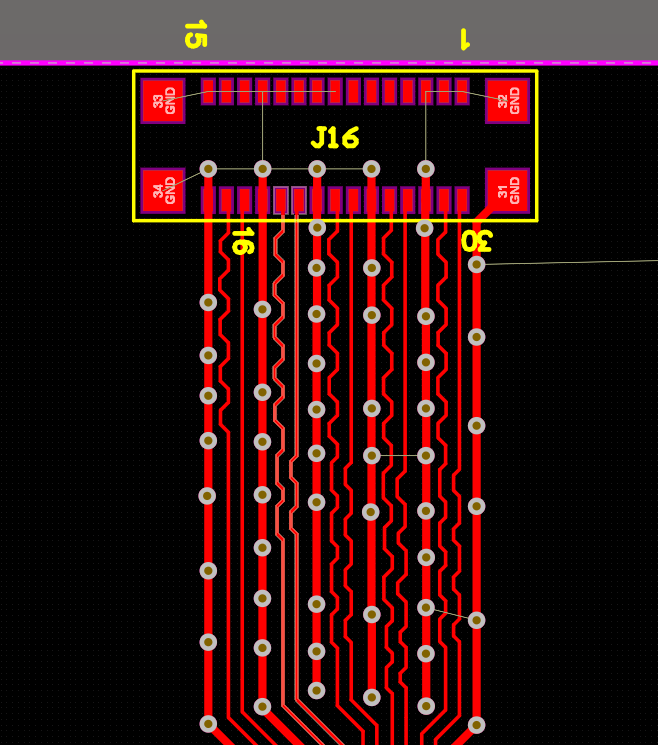

很多电子初学者在使用Cadence Allegro进行Layout设计时,会有一些MIPI或lvds等差分走线,在走线时可能为了匹配线序,导致信号网络的走线是交叉,这样做不仅费时费力,还会影响信号质量,那么如何将这些器件的引脚交换过来?如图

咨询一个问题呀,一个八层板上的MIPI加测试点的话,对显示影响大不大呀,主要是相机传感器的显示

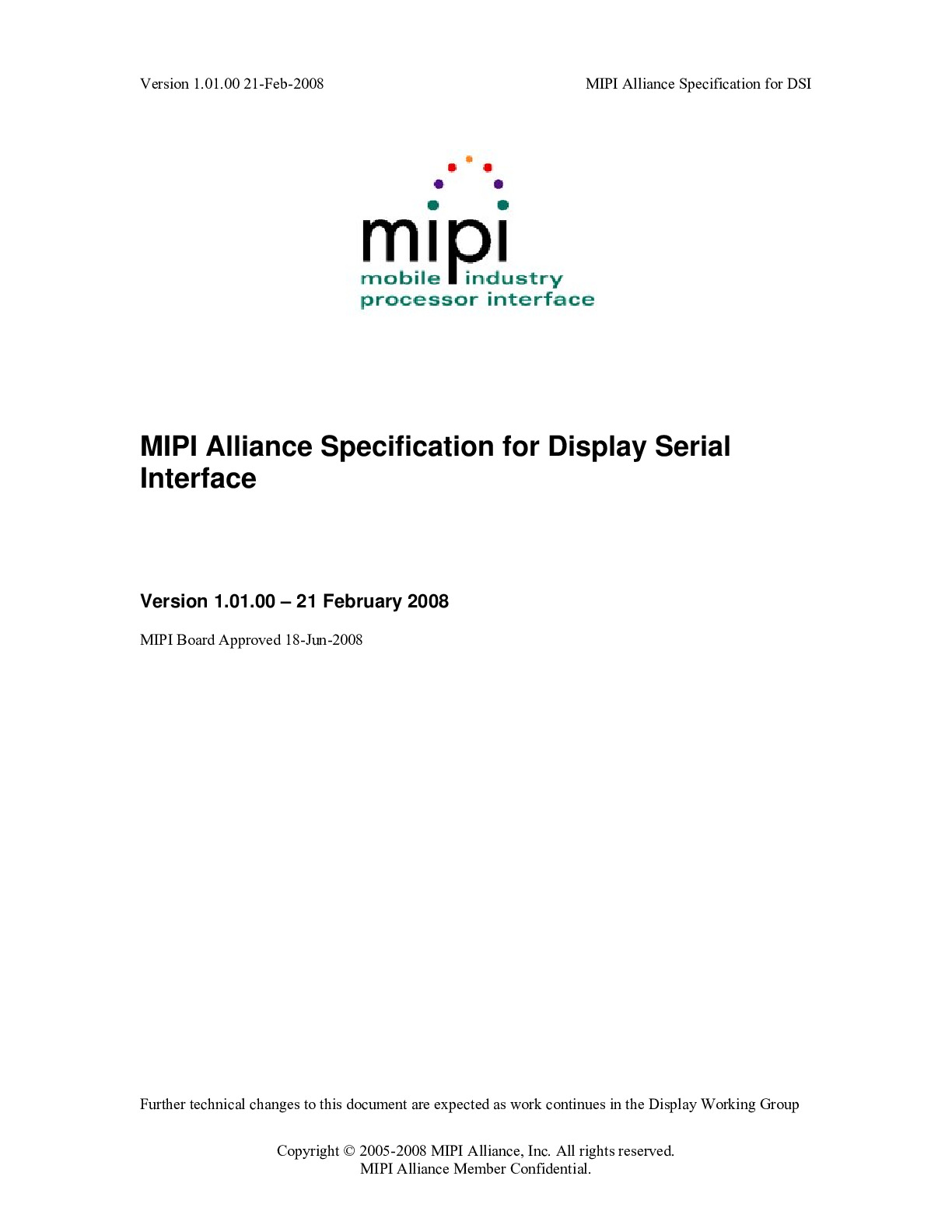

CrossLink-NX FPGA是首款采用Nexus技术平台设计的产品系列,为网络边缘开发工程师提供实现创新的嵌入式视觉解决方案所需的更低功耗、小尺寸和高可靠性。CrossLink-NX™ FPGA采用低功耗 28nm FD-SOI 技术

CrossLink-NX:用于嵌入式视觉处理的FPGA,可实现MIPI桥接和网络边缘AI。概述CrossLink-NX™ FPGA基于28nm FD-SOI Lattice Nexus平台。CrossLink-NX FPGA具有小尺寸、高可

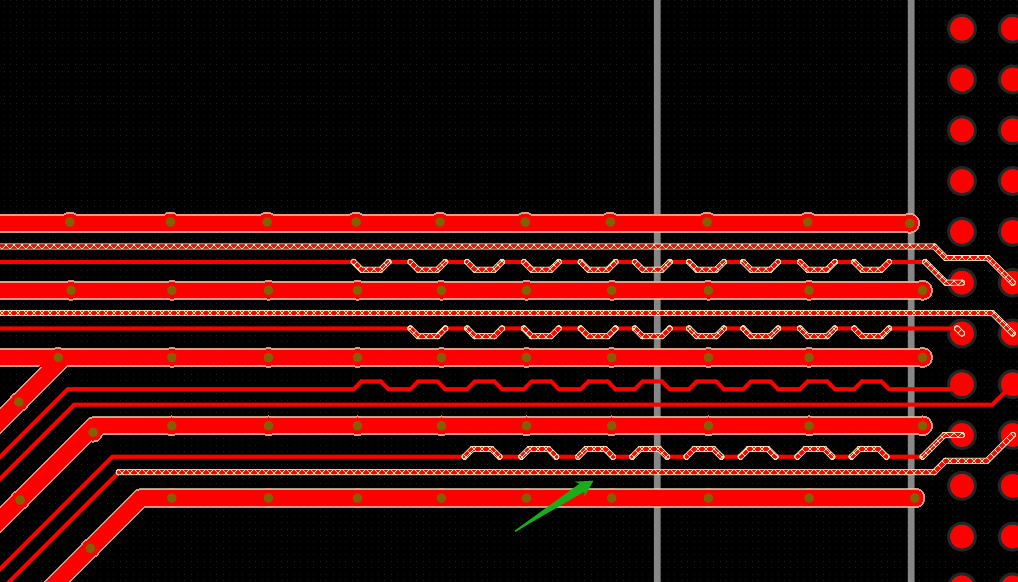

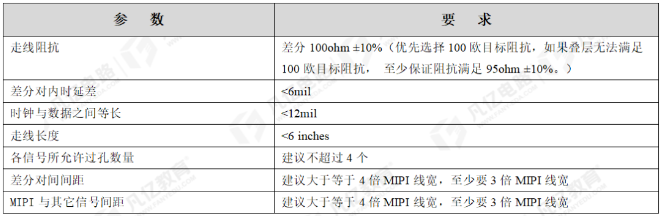

整板的GND网络并未连接,铺上大地铜连接即可:注意对内等长规范,GAP需要大于等于3W:将不符合规范的对内等长修改下。其他的差分对内等长以及对跟对等长没问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程

SATA:可以直接把差分规则里面的耦合度设置大一点就不会报错了:此处差分直接走顶层不用扇孔了:MIPI:注意差分组跟组等长误差为10MIL:此对差分对内等长误差是5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

很多电子工程师会选择MIPI接口进行通讯,但在使用过程中可能遇到不同问题,其中之一是:MIPI接口电平对不上,那么遇到这个问题,设备还能通讯吗?1、MIPI接口电平MIPI(Mobile Industry Processor Interfa

MIPI(移动行业处理器接口)是专为移动设备(如智能手机、平板电脑、笔记本电脑和混合设备)设计的行业规范的标准定义。其常见的通用的唯一物理(PHY)层,即MIPI D-PHY和C-PHY。MIPI D-PHY:更常用于智能手机的相机和显示屏

扫码关注

扫码关注