- 全部

- 默认排序

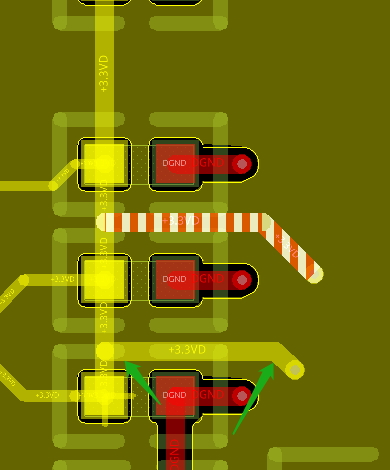

注意此处扇孔可以直接打在走线中间,这样拉出去形成了直角:注意个别过孔的间距,不要割裂了铜皮:注意数据组跟地址控制时钟组之间用GND走线隔开:再有空间的情况下 ,自己处理下。等长注意GAP尽量大于等于3W长度:优化处理下。其他的等长误差没什么

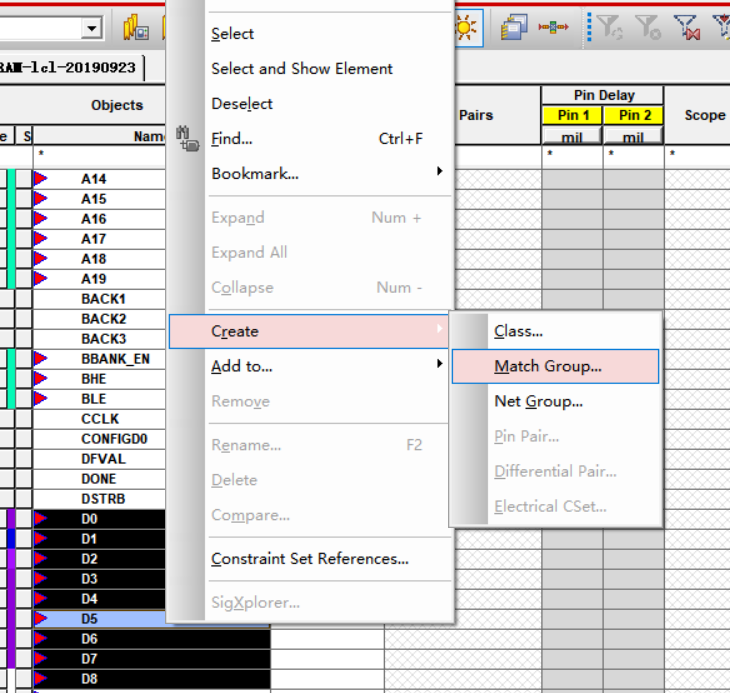

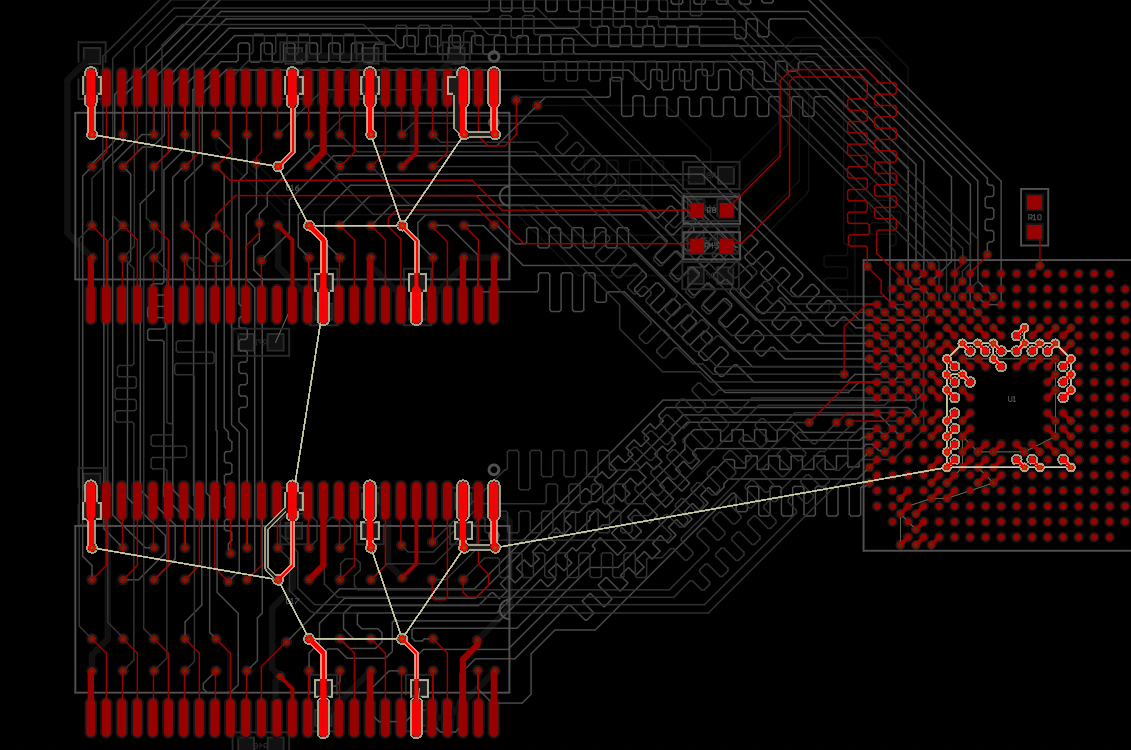

SDRAM信号线等长处理

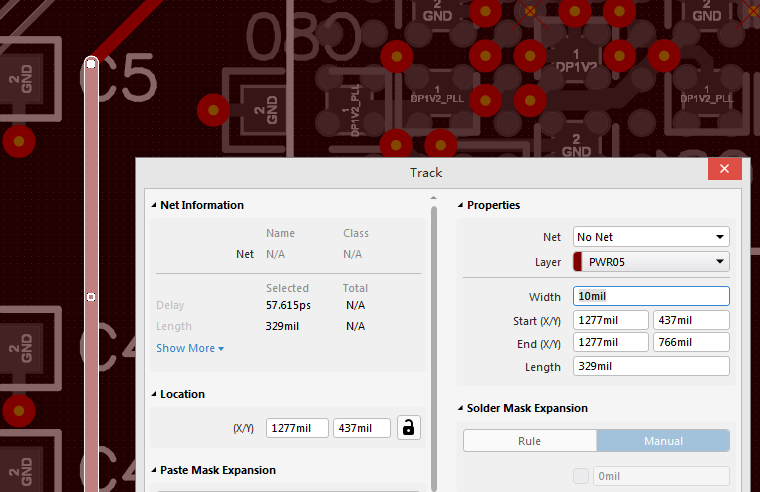

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

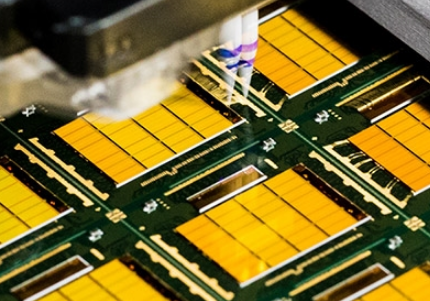

直播介绍:DDR SDRAM高速存储器是在高速PCB设计当中常见的模块,很多工程师对于如何处理单片、两片以及多片的布局、布线设计有很大的困惑,是一个设计难点。开设本次直播旨在全方位、多层次的去介绍DDR SDRAM高速存储器以及设计思路。直

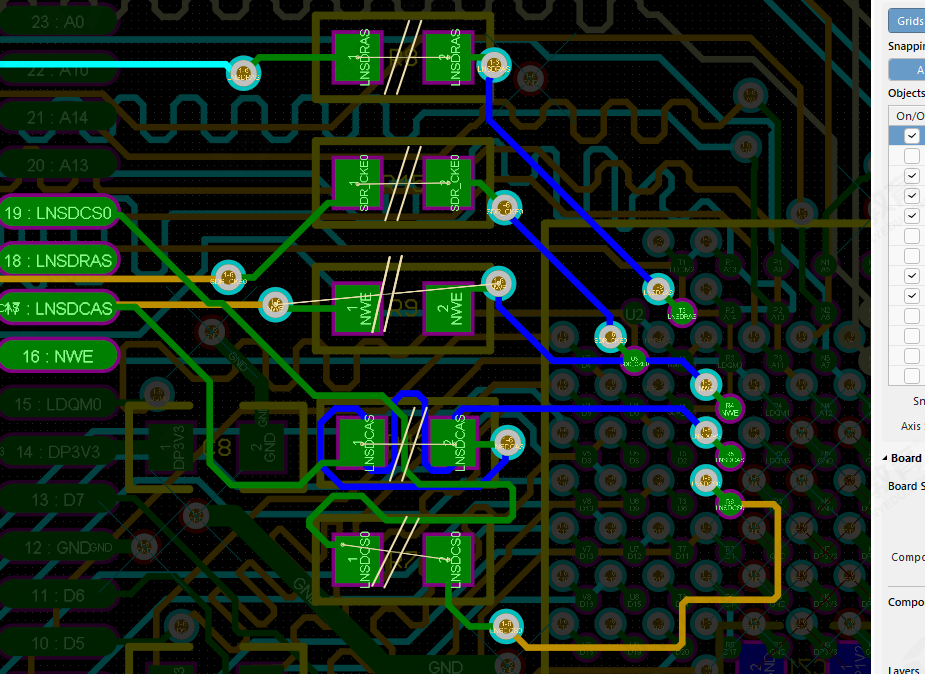

多处存在开路报错焊盘应从短边出线,避免从长边和四角出线ddr和芯片放置太近,导致没有足够空间绕线,绕线很乱走线不能从同层器件中间穿过时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

建议平面层的分割带宽度至少20MIL:地址信号类的等长还存在个别信号的误差报错:误差报错的信号自己再去等长优化。建议地址跟数据线两个类之间的信号可以走一根GND信号线进行分割开:或者自己预留20MIL的宽度。整个电源平面的信号都是3.3V信

数字经济时代,芯片扮演着重要角色。得益于人才聚集、产业升级、政策扶持等,我国的半导体产业正在蓬勃发展,并不断拉近与先进地区、企业的差距。日前,韩国研究机构OERI在报告中称,估计韩企和中国厂商在DRAM芯片的技术差距已缩短至5年。具体来说,

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

电源网络DP3V3全都是飞线显示,内层存在电源层赋予对应网络即可:电源平面层没有赋予网络,导致存在飞线网络没有连接:焊盘扇孔注意对齐,都没对齐,需要修改:类似这种过孔内存在线头的自己删除:注意走线优化:地址线内还存在误差报错:不需要拉线的地

数据线分组错误,一组应该是9根信号线2.注意数据线等长之间需要满足3W规则3.短接网络进行等长的,后期记得更新一下pcb,恢复正常网络4.地网络需要就近打孔,或者调整一下布局利用BGA里面地网络,尽量保证一个焊盘一个过孔以上评审报告来源于凡

扫码关注

扫码关注