- 全部

- 默认排序

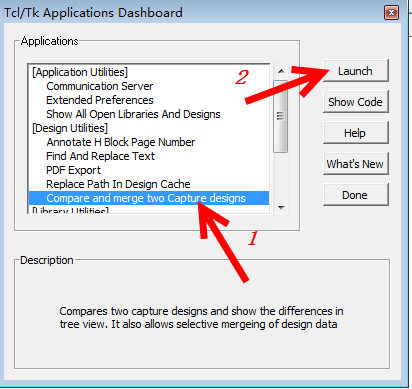

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

元件封装

求助!!在绘制封装时,在3D界面按shift+鼠标拖动,为什么立体图形不会旋转,只显示action no aviable in3D view ?C:\Users\李行\Desktop\12345678

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

在进行原理图设计时,可以为原理图上各种元素设置相应的颜色,如为连线、文本、背景、网络名等设置相应的颜色。也可以根据自己的设计习惯去分配颜色进行保存,以后在其他的原理图上都可以采用这个配色了。

在用Altium Designer画板子的时候,要生成gerber文件的时候,会出错,出现这样的提示框:出现"The Film is too small for this PCB"这个报错的主要原因就是菲林值的大小没有设置正确。

按照3D模型库添加库路径的方法添加完之后,打开PCB就提示错误。说steppath:variable not defined。需要进行怎么设置呢?C:\123.jpeg

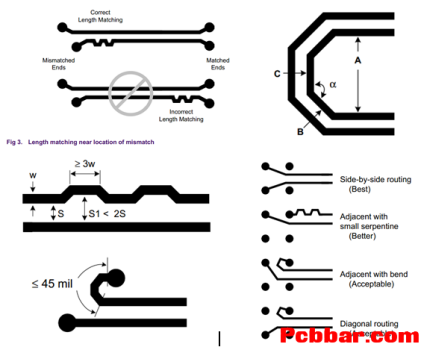

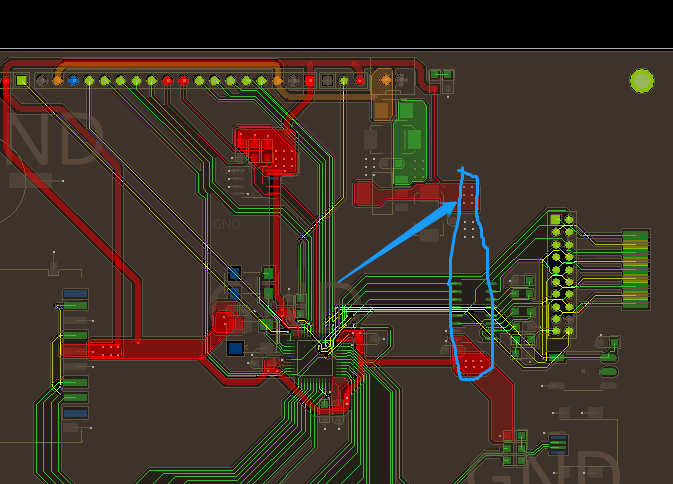

电源输出要从输出电容后面进行连接2.晶振需要包地处理,下面不要走别的信号线,包地需要打孔3.RS232 的升压电容走线需要加粗处理4.电源走线尽量加粗导20mil,满足载流5.USB尽量包地处理,并间隔100-150mil打上地过孔6.注意

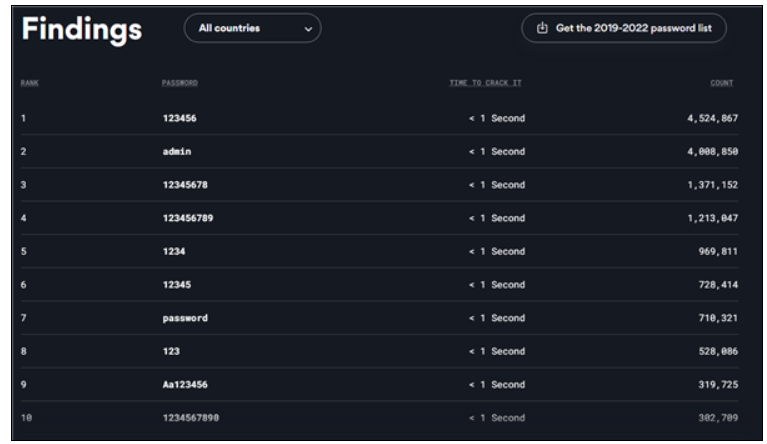

随着时代高速发展,密码逐渐成为了许多人的隐私保护手段之一,但有很多人设定的密码过于简单,很容易让人破解。最近,调研机构NordPass发布了2023年全球用户最长使用的200个密码,根据密码显示,其中123456以超过450万次数勇夺排行榜

了35000多名硬创先锋报名参加线上线下培训会,并成功聚集了400多家生态合作伙伴,与 500多家顶级投资机构建立合作。过往八届赛事123家总决赛晋级企业中,有112家获得融资,融资金额突破167亿,获2轮及以上融资的企业占比达54%。02

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注