- 全部

- 默认排序

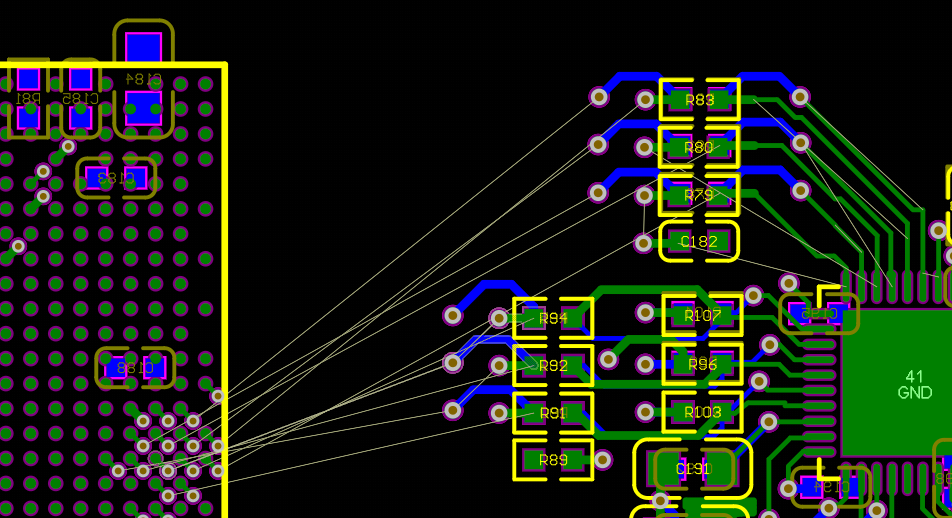

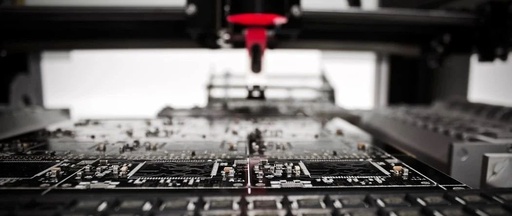

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

大家都知道,在PCB设计中要确保阻抗连续,但正如老祖宗所说的“人生总会有些意外”,如果PCB设计经常出现阻抗无法连续的情况,怎么办?谁来救救这个PCB板?遇到了这些问题,不如看看下面的方法?1、连接器处阻抗不连续①使用高质量的连接器:选择具

在电子工程中,很多电子小白会发现高速电路大都会配备电阻端接技术,以此解决信号反射、振铃等信号失真现象,这是为什么?能不能跳过这个操作?一般来说,高速电路中的信号传输速度非常快,相比其他电路,阻抗不连续性问题更加严重,当信号在传输过程中遇到阻

1.线宽要保持一致,线宽不一致会导致阻抗不连续。2.TF卡的时钟信号,与其他信号线的间距保证20mil左右,有空 间的情况下,包地处理。3.数据线等长错误,避免绕90度角等长。4.铺铜存在多处孤岛铜和尖岬铜皮以上评审报告来源于凡亿教育90天

作为PCB设计工程师,大家都知道阻抗要连续。但是,正如罗永浩所说“人生总有几次踩到大便的时候”,PCB设计也总有阻抗不能连续的时候,这时候该怎么办呢?关于阻抗先来澄清几个概念,我们经常会看到阻抗、特性阻抗、瞬时阻抗。严格来讲,他们是有区别的,但是万变不离其宗,它们仍然是阻抗的基本定义:a)将传输线始

作业未完成。很多布线、过孔没有网络,线宽不一致导致阻抗不连续、有直角。铜皮避让中间没连上,应该在铜皮属性栏换个链接方式。存在多处开路器件摆放干涉差分出线不耦合前后不一致,差分esd器件就近打孔差分走线不耦合,没有对内等长。变压器下面没有铺铜

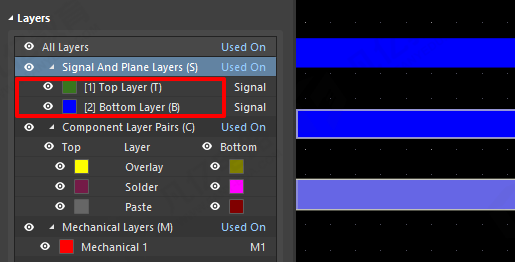

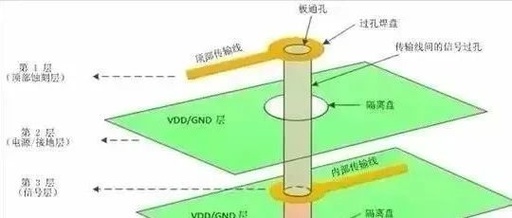

通孔在连接多层PCB的不同层上的走线方面起着导体的作用(印刷电路板)。在低频情况下,过孔不会影响信号传输。但是,随着频率的升高(高于1 GHz)和信号的上升沿变得陡峭(最多1ns),过孔不能简单地视为电连接的函数,而是必须仔细考虑过孔对信号完整性的影响。通孔表现为传输线上阻抗不连续的断点,导致信号反

作为PCB设计工程师,大家都知道阻抗要连续。但是,正如罗永浩所说“人生总有几次踩到大便的时候”,PCB设计也总有阻抗不能连续的时候,这时候该怎么办呢?关于阻抗先来澄清几个概念,我们经常会看到阻抗、特性阻抗、瞬时阻抗。严格来讲,他们是有区别的,但是万变不离其宗,它们仍然是阻抗的基本定义:a)将传输线始

在高频领域,信号或电磁波必须沿着具有均匀特征阻抗的传输路径传播。一旦阻抗失配或不连续现象,一部分信号被反射回发送端,剩余部分电磁波将继续被传输到接收端。信号反射和衰减的程度取决于阻抗不连续的程度。当失配阻抗幅度增加时,更大部分的信号会被反射

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

扫码关注

扫码关注