- 全部

- 默认排序

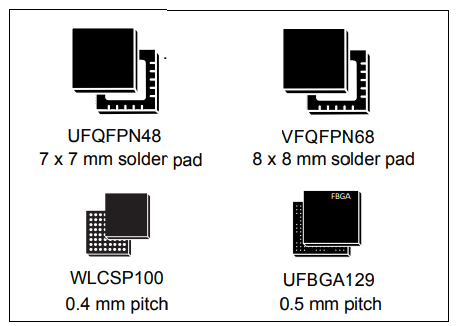

一、产品详情:STM32WB55xx 多协议无线和超低功耗器件内嵌功能强大的超低功耗无线电模块(符合蓝牙® 低功耗SIG规范5.0和IEEE 802.15.4-2011标准)。该器件内含专用的Arm® Cortex® -M0+,用于执行所有

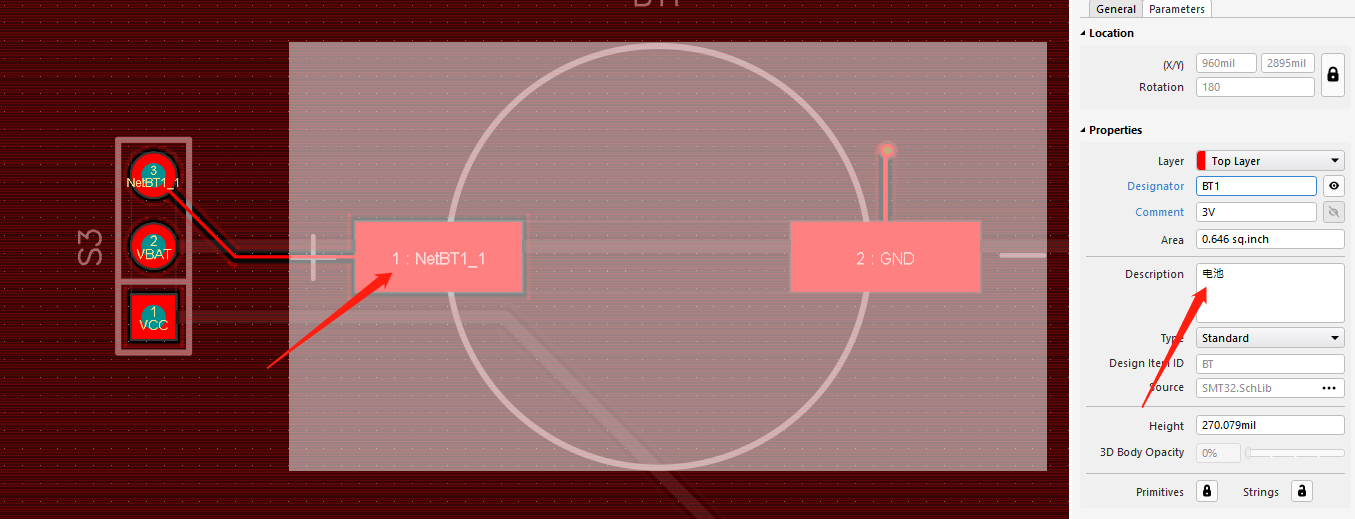

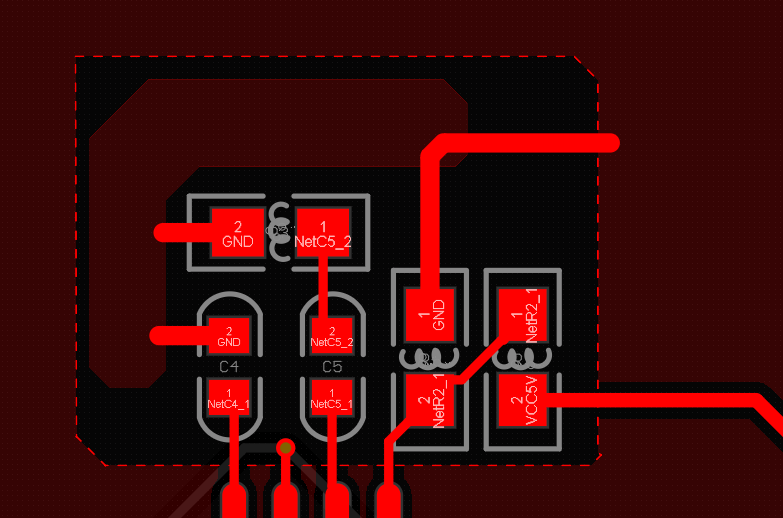

地缘信号走线需要加粗处理,尽量满足载流2.SD卡需要靠近板框放置3.SD卡信号线需要进行等长处理,误差300mil4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.晶振需要走内差分,并包地处理,在地线上均匀的打上地过孔

此处不用挖空,直接铺铜即可2.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.此处可直接铺铜包裹焊盘4.大电容摆放方向尽量保持一致,能对齐尽量对齐5.除了散热过孔其他的都可以盖油处理以上评审报告来源于凡亿教育90天高速P

高频电路设计问题要点

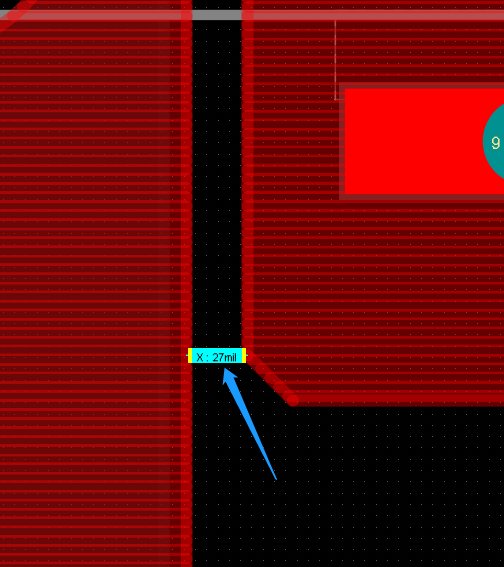

高频电路板设计学问就大了,注意的问题简单总结了以下几点: 1. 传输线拐角要采用45°角,以降低回损 2. 要采用绝缘常数值按层次严格受控的高性能绝缘电路板。这种方法有利于对绝缘材料与邻近布线之间的电磁场进行有效管理。 3. 要完善有关高精度蚀刻的PCB设计规范。电路设计要考虑规定线宽总误差为+/-0.0007英寸、对布线形状的下切(undercut)和横断面进行管理并指定布线侧壁电镀条件。对布线(导线)几何形状和涂层表面进行总体管理,对解决与微波频率相关的趋肤效应问题及实现这些规范相当重

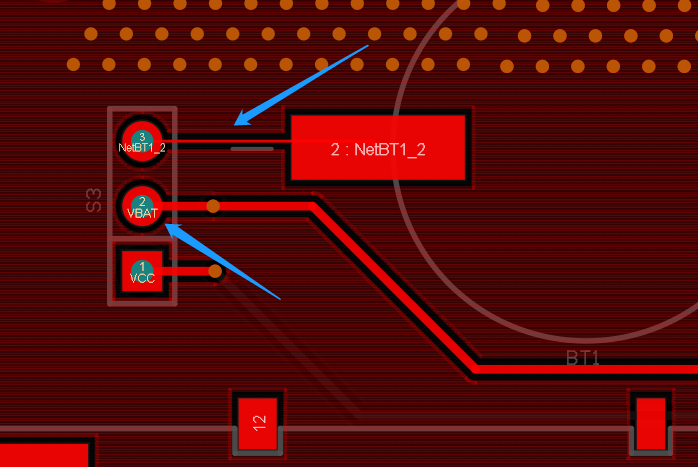

电源走线需要加粗,满足载流2.注意焊盘出线规范3.晶振需要包地处理,并打上地过孔,晶振下面不要走线4.走线与焊盘同宽,拉出焊盘在进行加粗处理5.232的升压电容走线需要加粗处理6.输出滤波电容先大后小摆放7.注意USB2.0有一对差分,对内

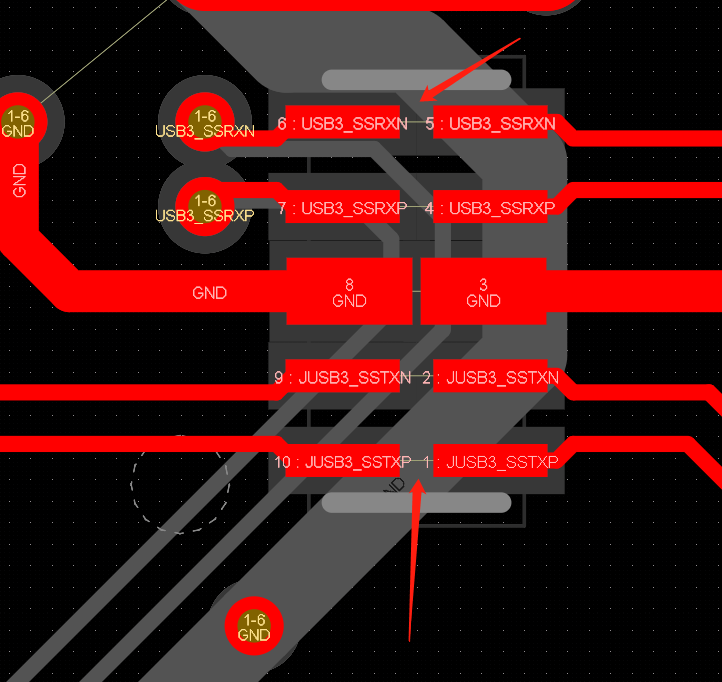

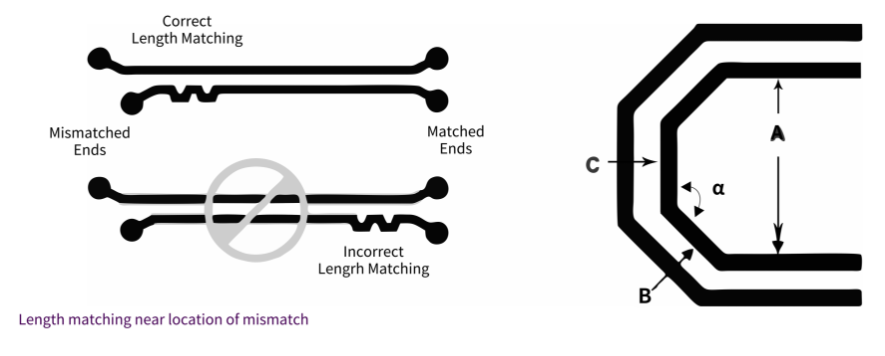

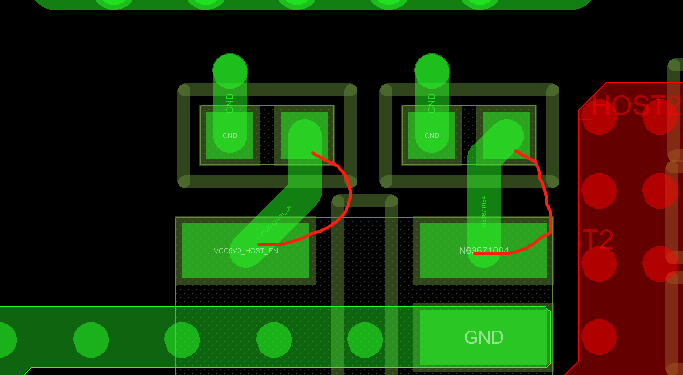

此处存在开路2.差分换层打孔尽量对齐,走线尽量耦合3.差分对内等长不规范,锯齿状等长不超过线距的两倍4.tpye-c差分对内等长误差5mil5.此处走线需要优化一下6.器件摆放尽量中心对齐7.过孔需要盖油处理以上评审报告来源于凡亿教育90天

分割地尽量满足1mm,有器件的地方不满足可以忽略2.跨接器件旁边尽量多打地过孔3.差分线需要优化一下,尽量从焊盘拉出在走差分差分出线方式都需要再尽量优化一下4.晶振需要包地处理,晶振下面不要走线,不要放置器件5.焊盘出现不规范,焊盘中心出线

中国作为全球产业链的重要环节,必须以协同的姿态迎接挑战,设计要考虑产品的制造成本和质量,早在70年代,在航天,通讯等机械领域就已开始了可制造性设计DFM的应用,电子行业是80年代后期引入的,HP公司DFM统计调查表明:产品总成本60%取决于产品的最初设计,75%的制造成本取决于设计说明和设计规范,70%~80%的生产缺陷是由于设计原因造成的。 电子可制造性设计DFM的实施,是有效建立产品的工艺路线图,缩短上市周期,减少产品质量风险,降低研发,试制,生产成本的有效思想。

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.差分走线不满足差分间距要求3.差分线处理不当,锯齿状等长不能超过线距的两倍差分都存在类似问题,后期自己针对进行修改4.线宽尽量保持一致5.差分走线尽量耦合,后期自己调整一下

扫码关注

扫码关注