- 全部

- 默认排序

ORCAD是兼容性很好的原理图设计工具,很多芯片原厂习惯性用这个软件来进行原理图设计,但是有PADS工程师来进行PCB设计的时候就不好直接导入了,那这个时候需要用到网表的输出和导入,为了更加方便ORCAD和AD软件同步PADS软件进行LAYOUT,这个视频讲解了ORCAD 和AD软件原理图怎样导出网表。

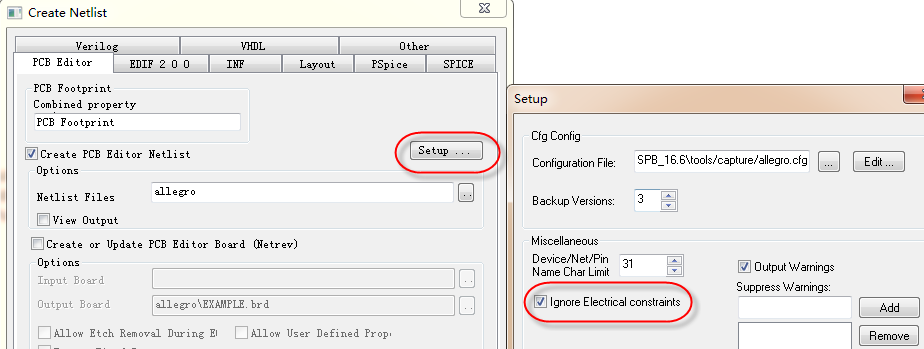

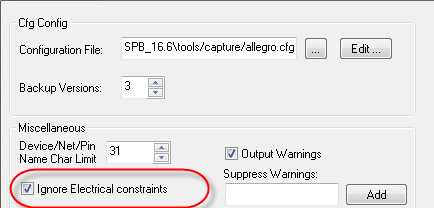

答:我们在进行PCB设计的时候呢,尽量不要把原理图的规则导入到PCB中,我们需要在输出网表的时候进行设置,具体的操作步骤如下所示:第一步,选中原理图的根目录文件即DSN文件,进行网表的输出,执行菜单Tools-Create Netlist,创建网表;第二步,在弹出的输出PCB网络表的对话框中,其它地方都是不用勾选的,在右侧有一个Setup选项,是输出网络的参数设置按钮,我们需要在这里进行不输出原理图规则的设置;第三步,点击输出网表的Setup选项,进行参数的设置,如图3-211所示,在左侧箭头所

答:我们在进行PCB设计的时候,都是在PCB布局完成之后,在PCB中进行规则设置,但是很多原理图工程师喜欢在原理图中设置规则,这样导入网表之后,PCB加入的规则就会被冲掉,我们这里讲解一下,如何不将原理图的中所添加的规则导入到PCB中,具体操作的步骤如下所示:

扫码关注

扫码关注