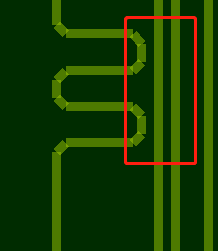

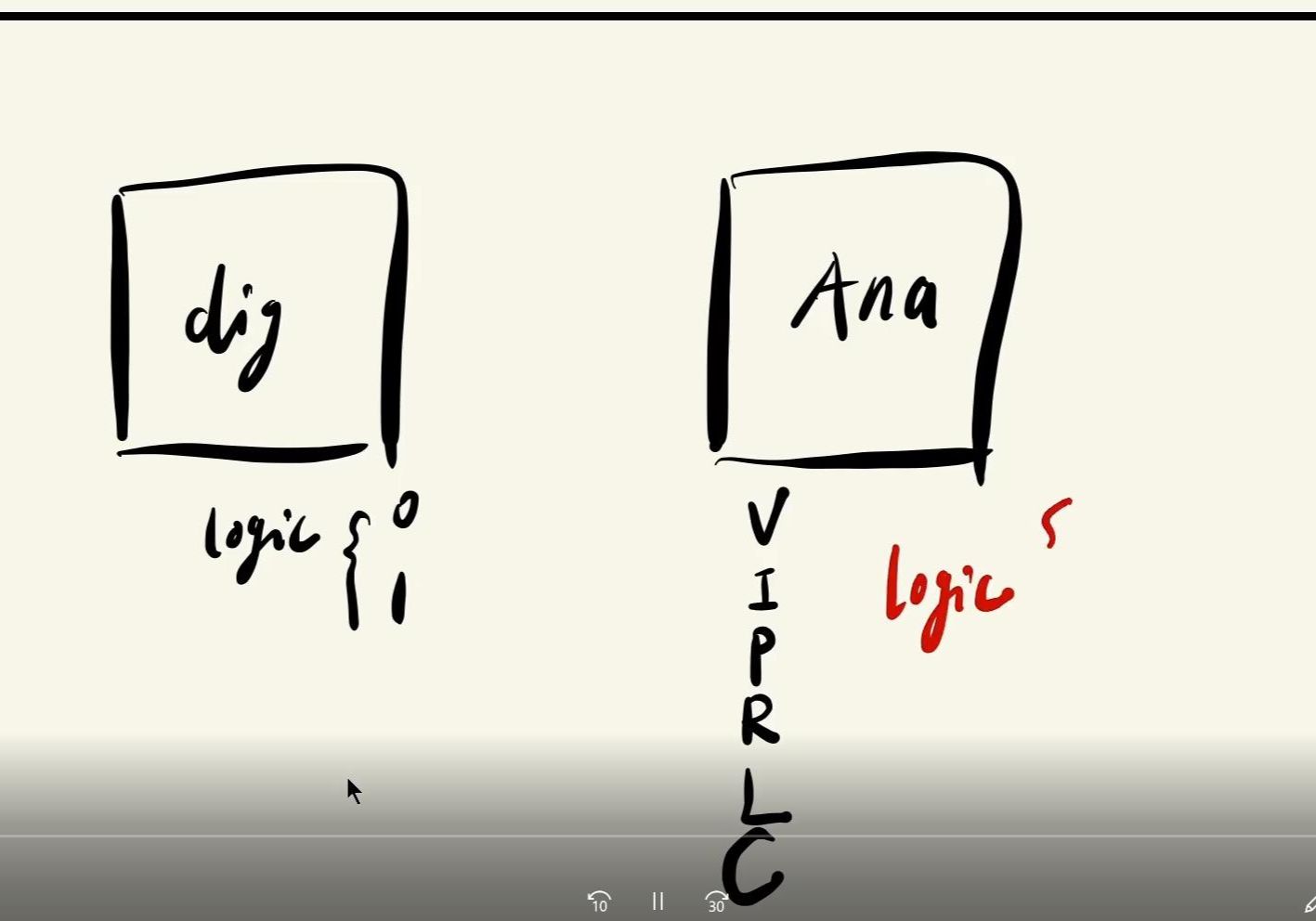

执行菜单命令file→export→logic.....如图:

弹出export logic对话框,选择design entry CIS选项,export directory选择输出网表的路径,然后单击export directory按钮。

导出完毕后,单击close按钮,关闭对话框。

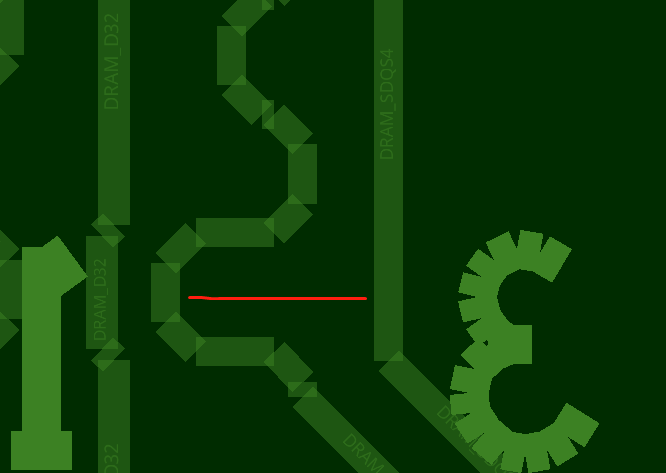

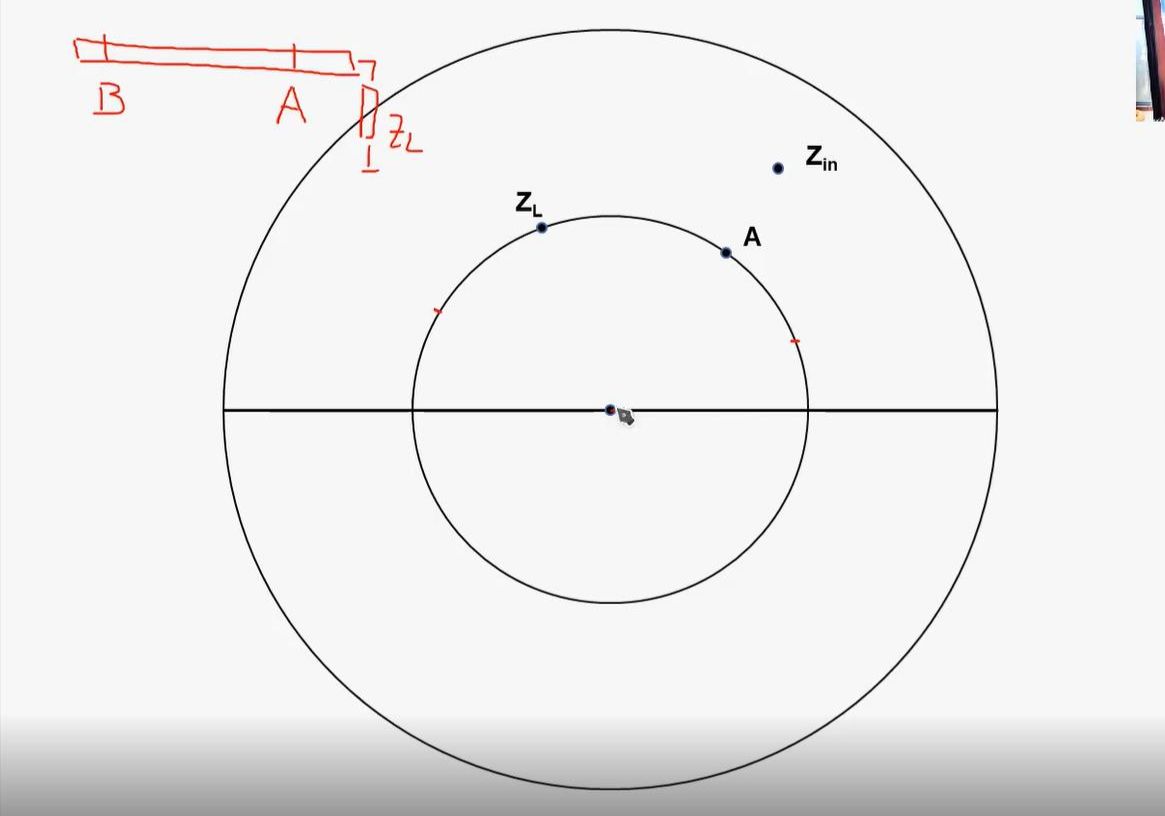

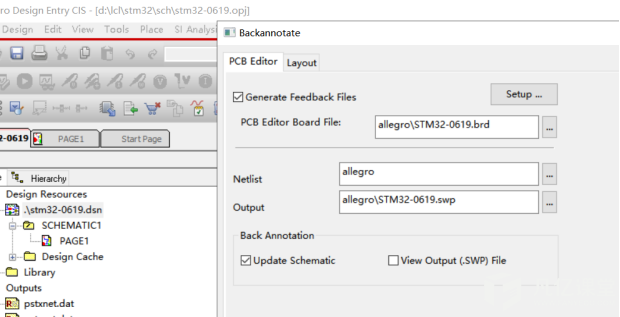

用orcad打开与PCB相对应的原理图,执行菜单命令tools→back annotate.....,在弹出的back annotate对话框中打开PCB editor选项卡,如图:

PCB editor board file:指定重新编号后的bar文件。

Netlist:指定bra导出的网表路径。

Output:指定输出的swap文件。

Update schematic:更新原理图。

View output(.SWP)file:浏览输出文件记录。

单击“确定”按钮,完成反标。

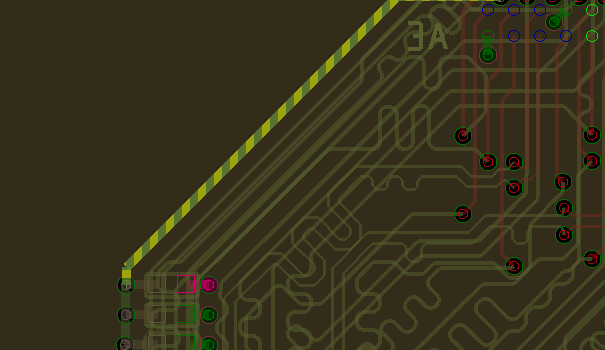

Cadence设计时一般不主张在PCB文件中更改网络连接关系,不过Auto rename仍然时非常实用的功能,按照布局重排位号,可以让PCB的丝印标识更清晰,容易检查,位号定位,方便维修。

扫码关注

扫码关注