- 全部

- 默认排序

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

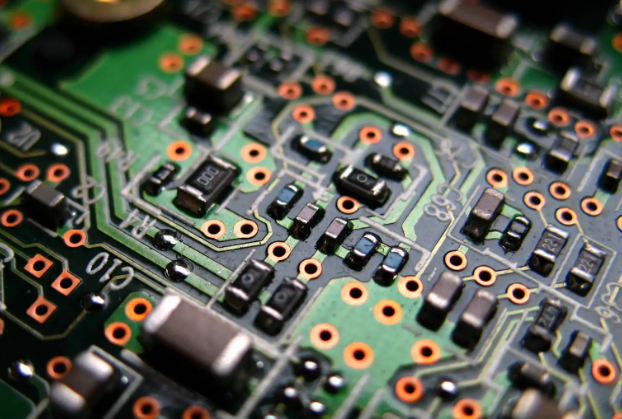

今天我们一起来了解下我们平时在PCB设计当中铺铜以及完成之后整版地铜皮的处理要点,我们一般我们在画完PCB之后都会在我们的PCB的外层和内层大面积的覆铜,这好像是一个共识,但是呢!其实这个覆铜也不能乱铺的,我们要针对不同的产品做不同的处理。

ReturnPath回流路径高速设计已成为愈来愈多PCB设计人员关切的重点。在进行高速pcb设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性问题。如果电流必须经过很长的路径才能返回,信号路径的电感回路会增加。当系统中的电感回路

在PCB设计中,布线布局是最重要的设计环节,然而很多工程师会把重点放在布线环节,经常忽略布局环节,这种思维是错误的,要尽量避免,若是没有良好的布局,如何在PCB板上更好的连接线路而不出错,所以今天我们来分享高速pcb设计的布局技巧及注意事项

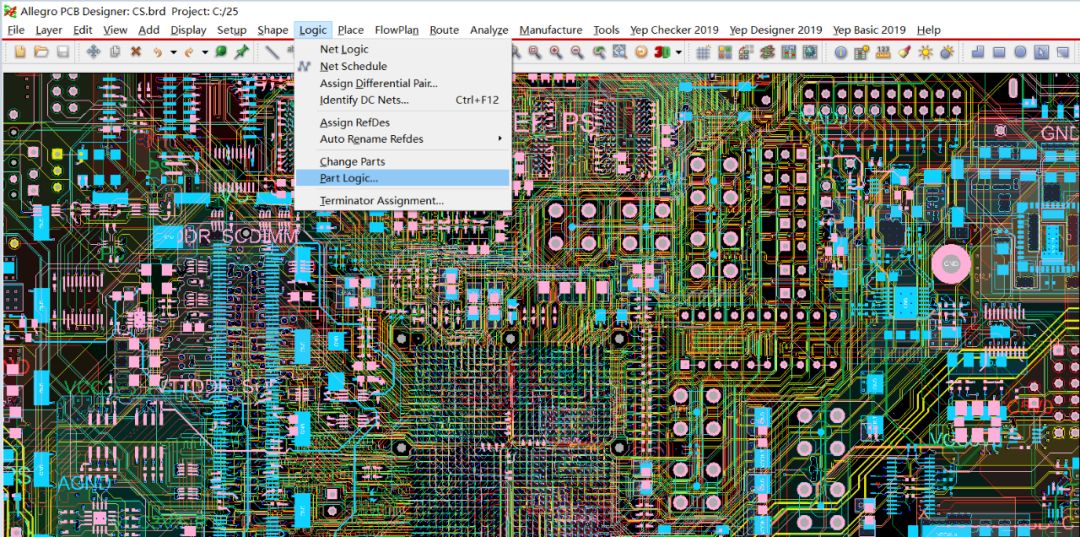

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速pcb设计用的最多工具,就是Allegro)。

之前我们分析了信号完整性和电源完整性,引起了很多读者的积极反响,所以今天来更新该系列的下篇,谈谈它们的重要因素,小伙伴要是想看上篇,可点击右侧链接《走进了解信号完整性和电源完整性(上)》。3、信号的振荡和环绕振荡和环绕的表现形式是信号反复出

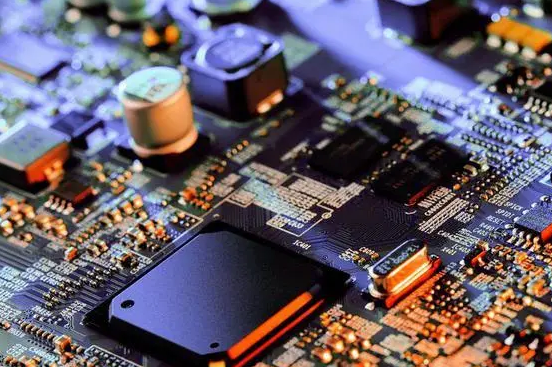

高速pcb设计在现代电子领域中扮演着很重要的角色,而高速PCB工程师的技能水平和经验对于项目的成功至关重要,下面本文将从地区分布、薪资水平、工作内容等多方面讨论对比不同等级的高速PCB工程师。1、初级高速PCB工程师①薪资水平初级高速PCB

接口电路和时钟电路是高速pcb设计中使用频率较高的两个电路,一直以来是电子工程师的重点知识,那么如何合理地做好借口电路和时钟电路的高速pcb设计的布局要求?下面来看看吧!1、接口电路的布局原则①接口信号的滤波、防护和隔离器件靠近接口连接器放

判断一个信号是否为高速信号首先要区分几个误区。误区一:信号周期频率FCLOCK高的才属于高速电路设计其实我们在电路设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率)Fknee。 如上图信号周期频率与有效(转折)频率定义为:(实际中多数信号)误区二:电容、电感式理想器件在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。但在高速领域,PCB上的电容电感等已经不能简单的视为纯粹的电容电感了。例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为F,则电容C

扫码关注

扫码关注