- 全部

- 默认排序

ReturnPath回流路径高速设计已成为愈来愈多PCB设计人员关切的重点。在进行高速PCB设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性问题。如果电流必须经过很长的路径才能返回,信号路径的电感回路会增加。当系统中的电感回路

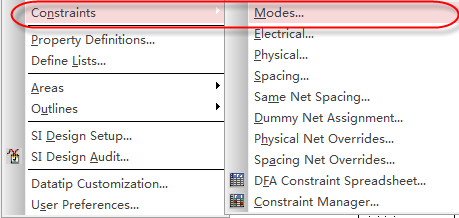

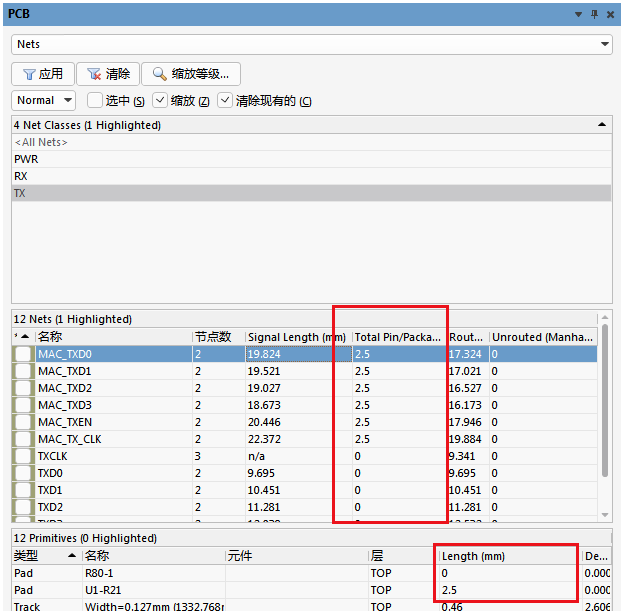

在高速设计中,基于时序的考虑通常要对信号做线长匹配。对于Allegro PCB设计者来说,我们在等长的时候经常会提到X-NET,利用X-NET功能我们能够很快的计算多点拓扑结构等长长度,并且还能够计算数据组等长误差,很是方便,但是我发现在给很多学员教学的过程中,很多人不清楚这个功能的使用,那么我们这次抽时间弄成一个专题来详细的给大家讲解一下。

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

在每一个超过500 MHz的高速设计中,连接介质,或连接到模具上的电线,都会给信号带来延迟。这种在设备中的延迟称为引脚延迟.即使从设计和PCB的角度来看,两个设备是完全兼容的,不同设备的封装延迟时间也会不同,所以它们需要考虑Pins信息。

Altium Designer 22X-Signal功能在Altium软件等长中的使用讲师:郑振宇直播直播:2022年5月27日 周五晚8点直播简介:在高速设计中,基于时序的考虑通常要对信号做线长匹配。对于Altium PCB设计者来说,我

我有几个问题,想请教下。

我有几个问题,想请教下。fpga的,普通io是什么电平标准呢ecl.还是cml,lvds,那种标准。因为,实际高速设计时需要通过电平标准,来设计匹配电路但我没在手册上,看到过相关描述

扫码关注

扫码关注