- 全部

- 默认排序

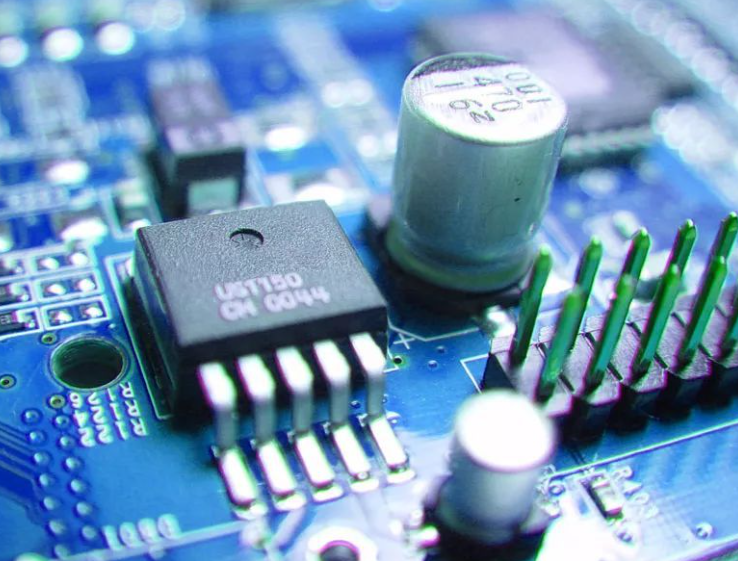

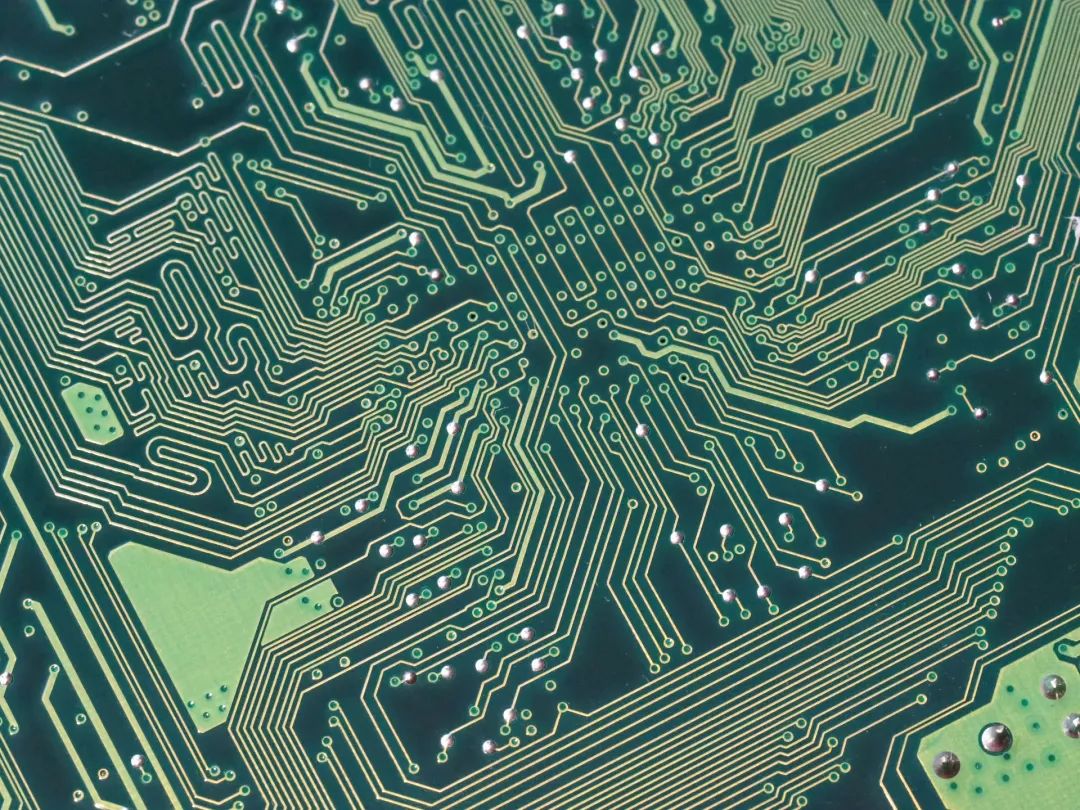

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

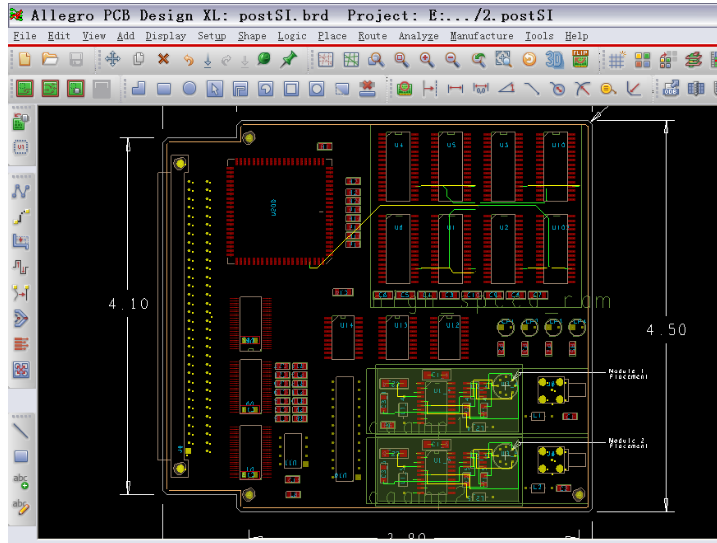

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

随着PCB板逐渐高密度化、性能化,导致信号速度的提高和板子尺寸的缩小,信号完整性(SI)和电源完整性(PI)分析变得愈发重要,但调试难度也大大增高。“了解SI&PI仿真?SI&PI仿真有何用?如何做好SI&PI仿真?”等已成为很多工程师需要

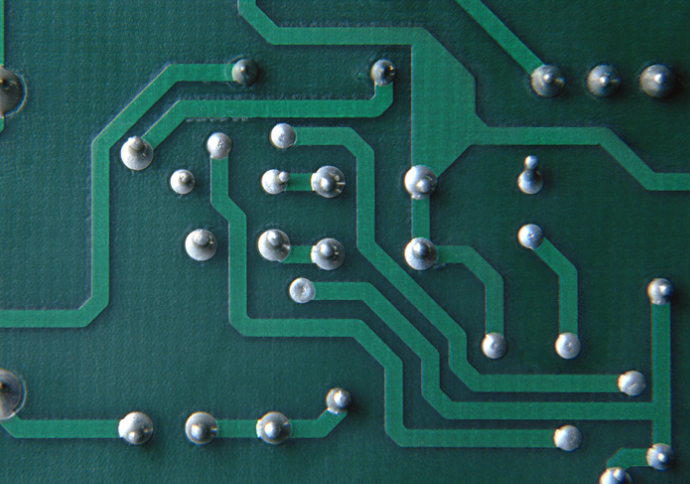

OSP是印刷电路板(PCB)铜箔表面处理的符合RoHS指令要求的一种工艺。1、引言PCB是现代电子产品不可缺少的材料,随着表面贴装技术(SMT)、集成电路(IC)技术的高速发展, PCB需要满足高密度、高平整化、高可靠性、更小孔径、更小焊盘的发展要求,对PCB表面处理和制作环境的要求也越来越高。OS

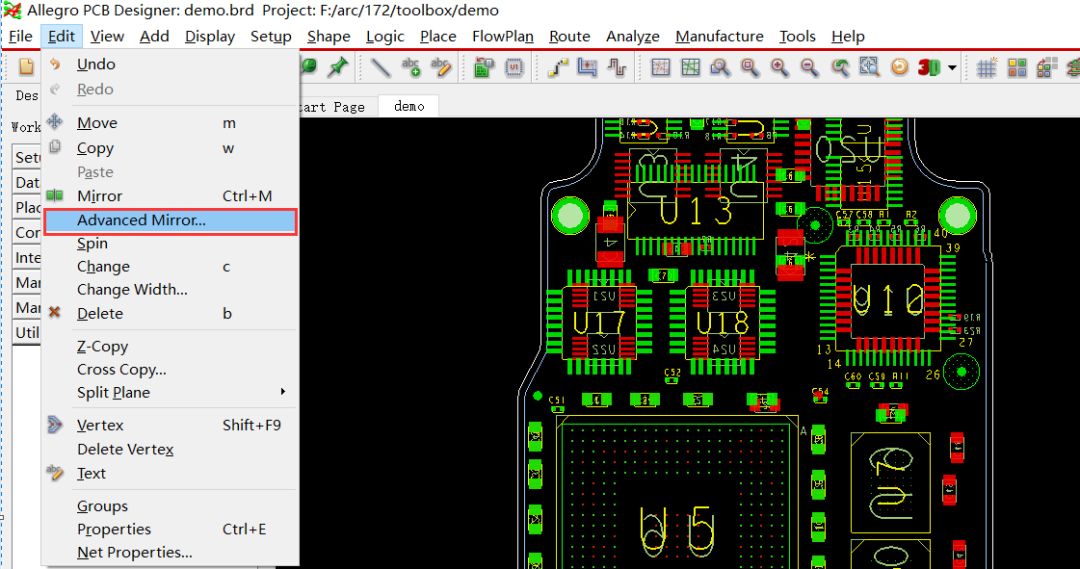

Allegro PCB Designer是一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。 在这个专题中,我们将介绍在该套件下的一个Toolbox选项组件下的Advanced Mirror高级镜像功能。

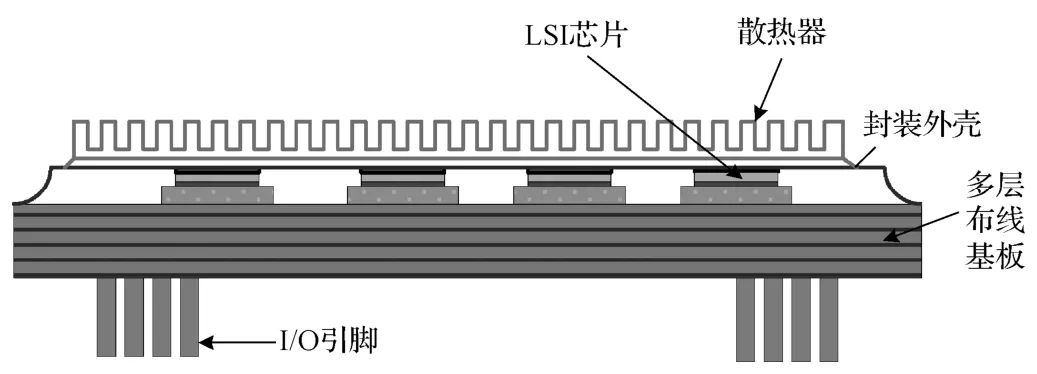

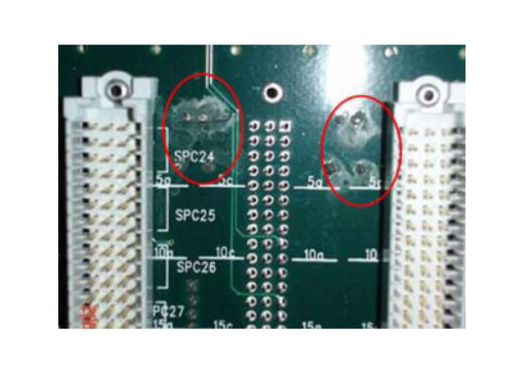

本篇内容根据《电子微组装可靠性设计》改编,本篇的思维导图如下电子微组装可靠性设计的挑战,来自两个方面:一是高密度组装的失效与控制;二是微组装可靠性的系统性设计。一、高密度组装的失效与控制高密度组装的代表性互连模式有两类,一类是元器件高密度组装,有两种典型的芯片组装方式,即芯片并列式组装(2D)和3D

随着电子产业的高速发展,PCB逐渐“高密度化、高性能化”,为了保证满足当代需求,越来越多厂商选择干膜来替代湿膜来完成图形转移等,干膜的使用越来越普及,但在使用干膜时很容易遇见破孔、渗镀等问题,如何解决?1、PCB干膜出现破孔问题怎么解决?很

Cadence Allegro现在几乎已成为高速板设计中实际上的工业标准,最新版本是Allegro 17.4。与其前端产品Capture相结合,可完成高速、高密度、多层的复杂 PCB 设计布线工作。

一、PCBA多余物1.多余物定义PCBA制造过程中所发生的,存在于机内的所有非设计和工艺所要求的各种物理的或化学的、可见的和不可见的、气态的或液态的、宏观的或微观的等物质,均属多余物。多余物是产品潜在的可靠性隐患,必须仔细地清除。特别是对高密度组装和高可靠性产品来说,保持产品的清洁度要求尤为重要。2

随着时代高速发展,越来越多电子工程师开始放弃PCB单面板设计,选择多层板设计,这是由于多种因素及市场所决定,那么我们来看看为什么PCB多层板设计越来越受欢迎?1. 高密度集成电路现代电子产品求更高的性能和更小的尺寸。高密度集成电路(IC)变

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第二部]](https://api.fanyedu.com/public/uploads/image/course/20200518/92b8de8dc1073a42c2d24b16c709e55e.jpg)