- 全部

- 默认排序

SiP失效模式和失效机理

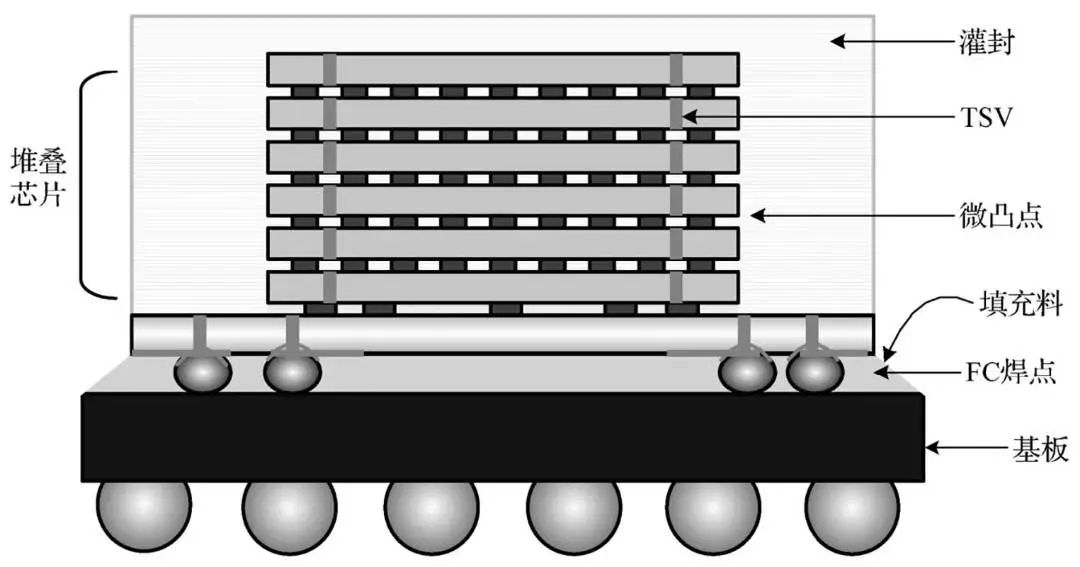

SiP组件的失效模式主要表现为硅通孔(TSV)失效、裸芯片叠层封装失效、堆叠封装(PoP)结构失效、芯片倒装焊失效等,这些SiP的高密度封装结构失效是导致SiP产品性能失效的重要原因。一、TSV失效模式和机理TSV是SiP组件中一种系统级架构的新的高密度内部互连方式,采用TSV通孔互连的堆叠芯片封装

原来当我在研究实验室工作并为我们的电喷控制系统设计PCB时,我的布局很糟糕。因为当时我们并不担心外包装机箱,以及有限的电路板空间或必须紧凑的布线等小问题。只要我们能够将所有必需的元器件放在电路板上并最终将电路板实现成为物理印刷电路,我们就已经很满足了。

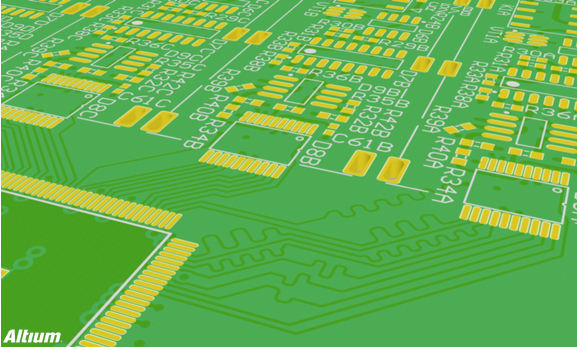

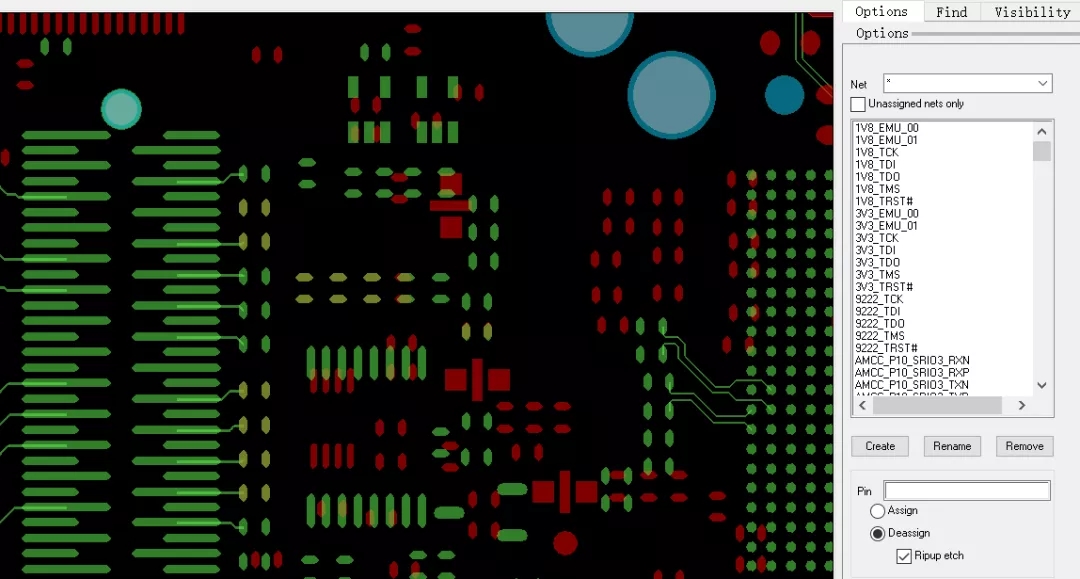

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

多层PCB内部长啥样?

硬件工程师刚接触多层PCB的时候,很容易看晕。动辄十层八层的,线路像蜘蛛网一样。画了几张多层PCB电路板内部结构图,用立体图形展示各种叠层结构的PCB图内部架构。高密度互联板(HDI)的核心在过孔多层PCB的线路加工,和单层双层没什么区别,

【直播时间】11月4日 晚8点【直播介绍】在开关电源设计时,设计工程师经常会碰到由于接地点设计不合理,导致设计的产品存在EMI的问题,本次直播从电磁干扰产生的根源和大家分析产生地弹的原因,并且给大家介绍优化、减小地弹的设计方法及思维。【直播大纲】1、BUCK拓扑结构电路介绍 2、BOOST拓扑结构电路介绍3、如何减小设计时地弹影响 4、交流互动,问题解答【讲师介绍】龙学飞:PCB联盟网电子论坛特邀版主,凡亿技术PADS、封装课程金牌讲师,熟练使用Allegro、PADS、AD等EDA设计软件,10年+高速PCB设计与EDA培训经验;具备丰富的高速高密度PCB设计实践和工程经验,擅长消费类电子、高速通信等各类型产品PCB设计,擅长PCB封装库设计与管理,有丰富CIS系统(零件物料信息系统)设计与管理经验。

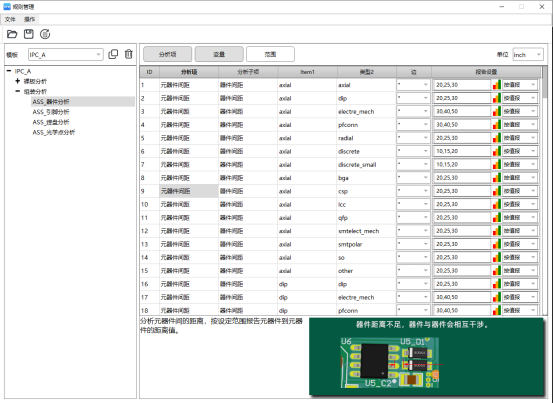

“SMT贴片加工逐步往高密度、细间距的设计发展,元器件的最小间距设计需考虑smt厂家的经验程度和工艺是否完善。元器件最小间距的设计除了保证smt焊盘间不易短接的安全间距外,还应考虑元器件的可维护性。”元器件布局为什么要保证安全间距?1安全距

随着PCB板逐渐高密度化、性能化,导致信号速度的提高和板子尺寸的缩小,信号完整性(SI)和电源完整性(PI)分析变得愈发重要,但调试难度也大大增高。“了解SI&PI仿真?SI&PI仿真有何用?如何做好SI&PI仿真?”等已成为很多工程师需要

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

OSP是印刷电路板(PCB)铜箔表面处理的符合RoHS指令要求的一种工艺。1、引言PCB是现代电子产品不可缺少的材料,随着表面贴装技术(SMT)、集成电路(IC)技术的高速发展, PCB需要满足高密度、高平整化、高可靠性、更小孔径、更小焊盘的发展要求,对PCB表面处理和制作环境的要求也越来越高。OS

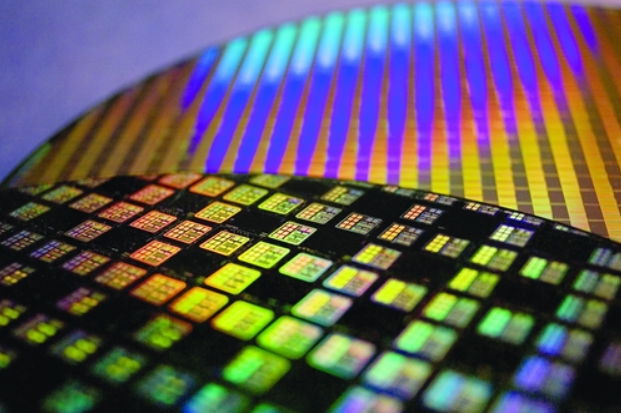

众所周知,光刻机被誉为“芯片之母”,在芯片制造过程中扮演着至关重要的角色,造价昂贵,数量稀少,因此是高精度高密度的尖端设备,发展多年,至今只有ASML可生产先进工艺的光刻机。近日,俄罗斯公开表示正在研发光刻机,最快将在2024年出成果,据俄

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第二部]](https://api.fanyedu.com/public/uploads/image/course/20200518/92b8de8dc1073a42c2d24b16c709e55e.jpg)