- 全部

- 默认排序

当对allegro软件PCB层叠结构进行设置的时候,某一层可以设置为plane或者conduct,平面层和走线层。但是我发现无论是设置成plane还是conduct,这一层都可以走线,手动铺铜皮,edit-split creat这样去灌铜进行铜皮分割。既然这样,那么设置层的时候,plane和cond

简介:使用FR4敷铜板PCBA上各个器件之间的电气连接是通过其各层敷着的铜箔走线和过孔来实现的。由于不同产品、不同模块电流大小不同,为实现各个功能,设计人员需要知道所设计的走线和过孔能否承载相应的电流,以实现产品的功能,防止过流时产品烧毁。文中介绍设计和测试FR4敷铜板上走线和过孔的电流承载能力的方

什么是规则?各类器件到器件应该控制多少?走线的间距应该控制多少?铺铜的间距应该控制多少?这是很多工程师不清楚的问题所在,这就是规则的魅力。本次直播,从工程师的角度出发,全面解析如何去根据不同的板卡设置不同的规则,规则设置的要点在哪里,让大家可以全面掌握如何在高速PCB设计过程中合理的设置以及利用规则。

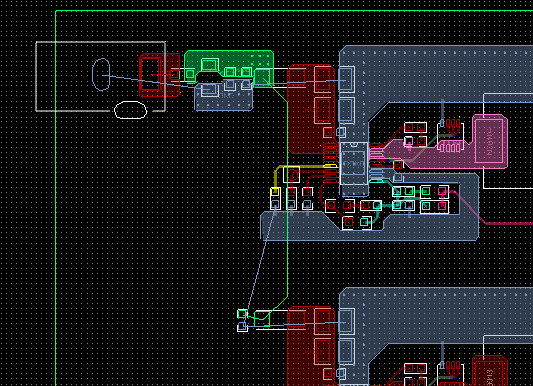

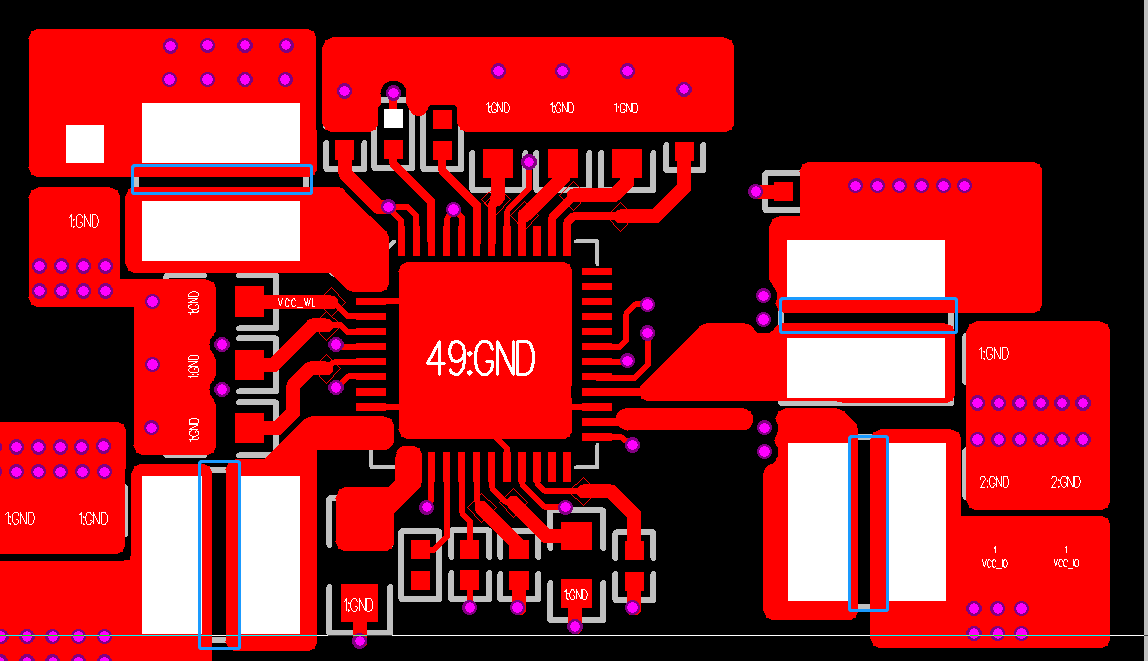

有飞线未连接铜皮没有分配网络铺铜可以调整一下要包住焊盘这里可以铺铜连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.ht

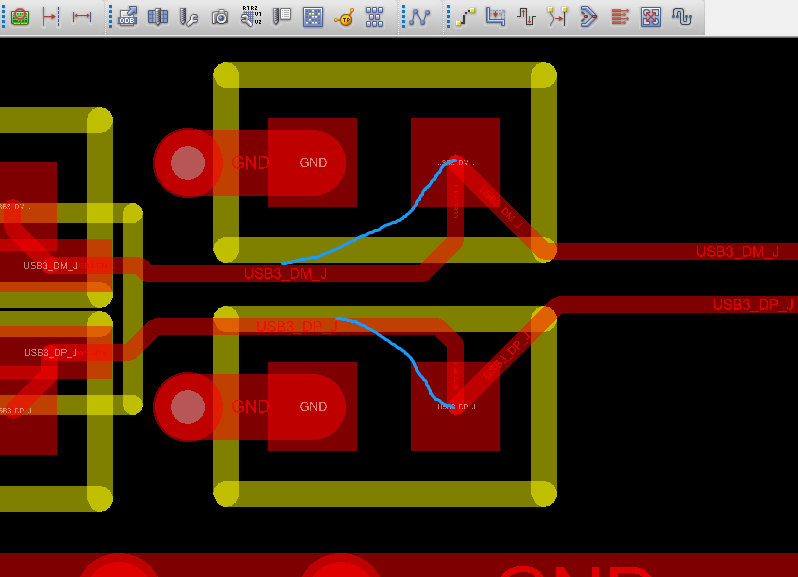

差分出线可以在尽显一下优化2.差分走线要尽量耦合3.差分走线不满足差分间距要求4.锯齿状等长不能超过线距的两倍5.存在开路后期自己在地平面层铺一下整版铜,把地尽量连接6.线宽尽量保持一致7.USB差分对内等长误差5mil以上评审报告来源于凡

1.线宽要保持一致,线宽不一致会导致阻抗不连续。2.TF卡的时钟信号,与其他信号线的间距保证20mil左右,有空 间的情况下,包地处理。3.数据线等长错误,避免绕90度角等长。4.铺铜存在多处孤岛铜和尖岬铜皮以上评审报告来源于凡亿教育90天

电感所在层的内部需要挖空2.滤波电容靠近电源输入管脚,走线加粗3.反馈路劲走一根10mil的线即可4.此处为输入主干道,打一个过孔不满足载流,建议铺铜处理5.确认一下此处输出主干道是否满足载流6.pcb上存在DRC以上评审报告来源于凡亿教育

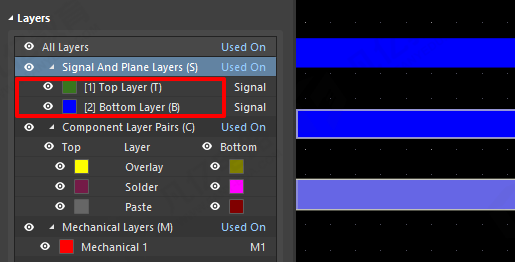

一个学习信号完整性仿真的layout工程师我们在进行PCB设计时,会经常与板厂打交道,其中最重要的一个概念就是PCB的层叠,它关系到layout的阻抗控制。不同的板厚,每层的的PP和copper的厚度是不一样的。其中的copper,也就是常

扫码关注

扫码关注