- 全部

- 默认排序

有个问题想请教一下,设计6层板的时候将2,5层设置成电源层,3,4层设置成内部布线层。这样两层之间难免有一些线会重叠部分,怎么确认会不会有严重的串扰?

在使用allegro绘制蛇形天线封装的时候,天线本体是焊盘1,馈点是焊盘2叠加在焊盘1上,导致报错无法生成PSM文件,请问怎么解决呢?

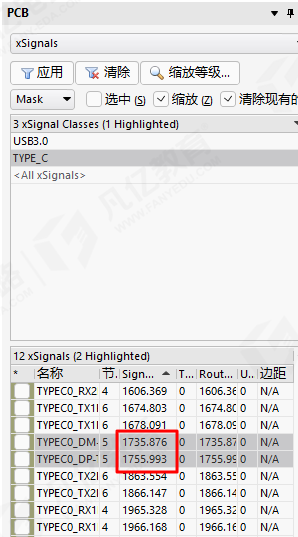

差分对内等长误差控制5mil范围内少设置一对差分对两个小器件之间器件不能干涉,丝印不要重叠以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.c

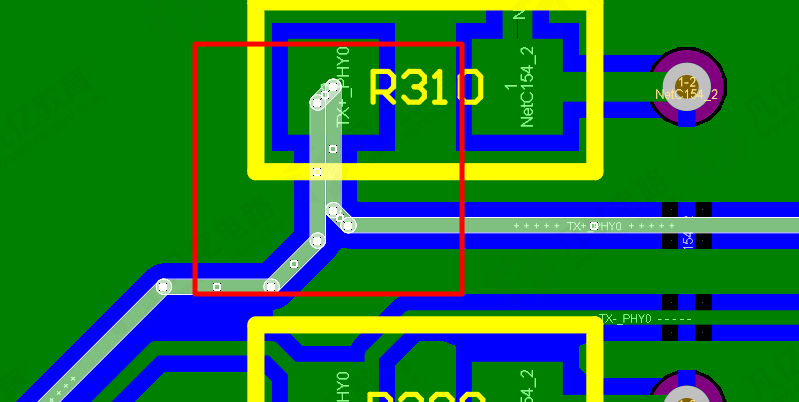

差分连接焊盘走线不要重叠、锐角,两边保持一致变压器除差分走线以外其他所有走线加粗到20mil以上差分走线尽量耦合差分走线出焊盘尽快耦合保持长度一致时钟信号包地打孔处理rx、tx分别建立等长组控制100mil误差分别等长走线应连接到焊盘中心,

在印刷电路板(PCB)设计中,很多电子工程师回遇到不少问题,今天本文将挑选工程师易犯的常见十大缺陷问题,希望对小伙伴们有所帮助。1、加工层次定义不明确2、单面焊盘孔径设置错误4、表面贴装器件焊盘太短5、字符乱放6、用填充块画焊盘7、焊盘重叠

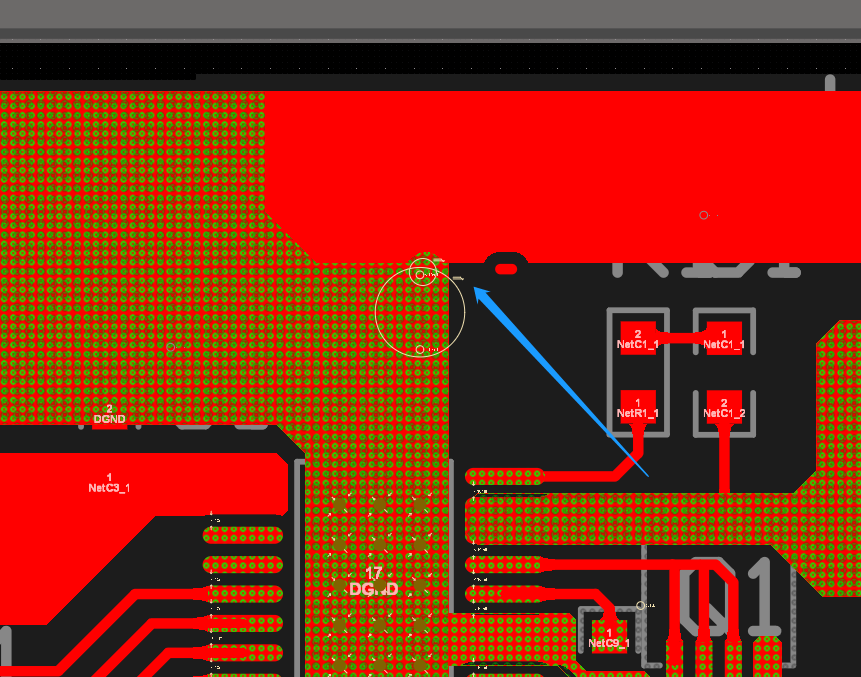

还存在网络并未连接完全,自己后期铺地铜进行连接:注意调整下器件位号丝印,不要覆盖在焊盘上或者是重叠,直接就近放在器件旁边整齐排列即可:过孔散热焊盘上的开窗即可,其他的盖油处理:铺铜注意不要有这种尖角:电感内部注意挖空处理:自己看下过孔都没网

还存在开路报错,自己检查修改下:电感当前层的内部注意放置挖空区域:注意主干道器件需要整体中心对齐,都没 对齐:根据电流输出方向,电容按照先大后小的顺序布局,布局有问题:器件丝印位号没有放置整齐,要不在板外,要不就丝印重叠或者丝印覆盖焊盘了,

注意一脚标识不要跟器件重叠了,注意调整下:注意电源信号的线宽是否满足载流:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.

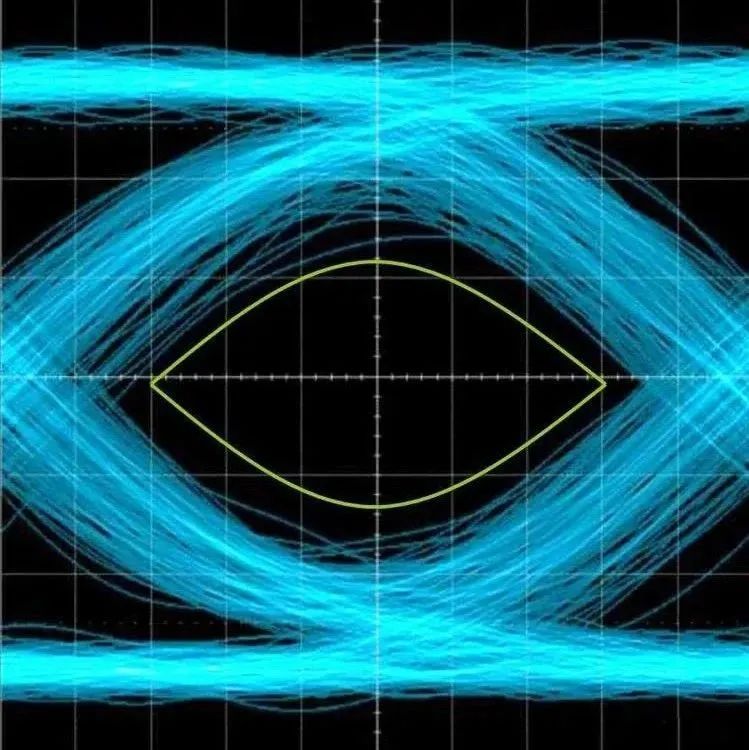

什么是眼图?

眼图,是由于示波器的余辉作用,将扫描所得的每一个码元波形重叠在一起,从而形成眼图。本文将带领大家了解PCB上的眼图是什么,眼图是怎样形成的,眼图中包含有哪些信息,如何根据眼图情况分辨信号质量。想看懂示波器眼图需要掌握以下4点:一、什么是眼图?眼图是一系列数字信号在示波器上累积而显示的图形,它包含了丰

扫码关注

扫码关注