- 全部

- 默认排序

其实对于一个开关电源工程师而言,PCB的绘制其实是对一款产品的影响至关重要的部分,如果不能很好地Layout的话,整个电源很有可能不能正常工作,最小问题也是稳波或者EMC过不去。 这是一个成品开关电源模组,文章会以这个电源模组的设计重点给大家讲一些点。经验一,安规走线间距这个是写在协议里面的,如果

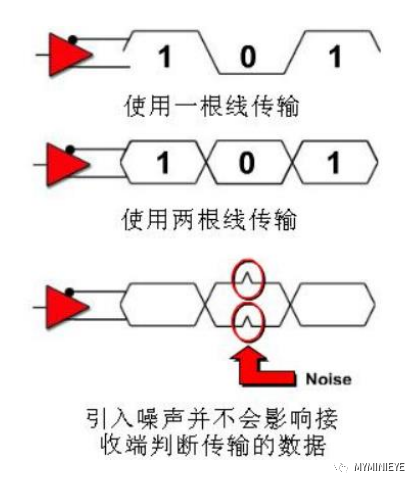

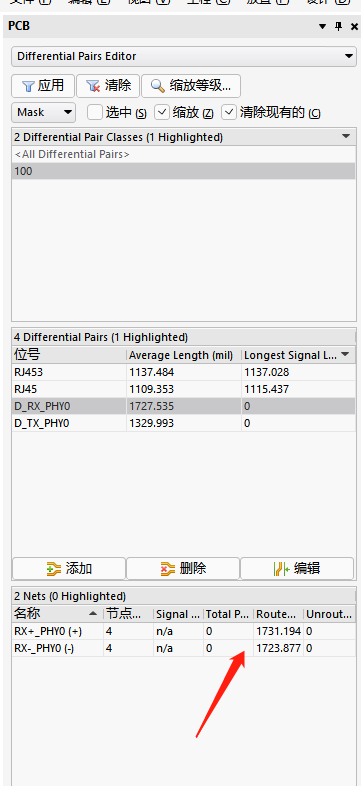

1、差分信号简介1.1 差分信号区别于传统的一根信号线一根地线的做法,差分传输在两根线上都传输信号,这两个信号的振幅相同,相位相反,在这两根线上的传输的信号就是差分信号。信号接收端通过比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线

蛇形走线和码间干扰是高速PCB设计中需要关注的两个重要问题,在布线阶段若是没处理好蛇形走线和码间干扰,容易影响到系统性能和稳定性,下面讲讲如何处理这两个问题,希望对小伙伴们有所帮助。蛇形走线是一种常用的布线方式,可以降低信号线之间的互相干扰

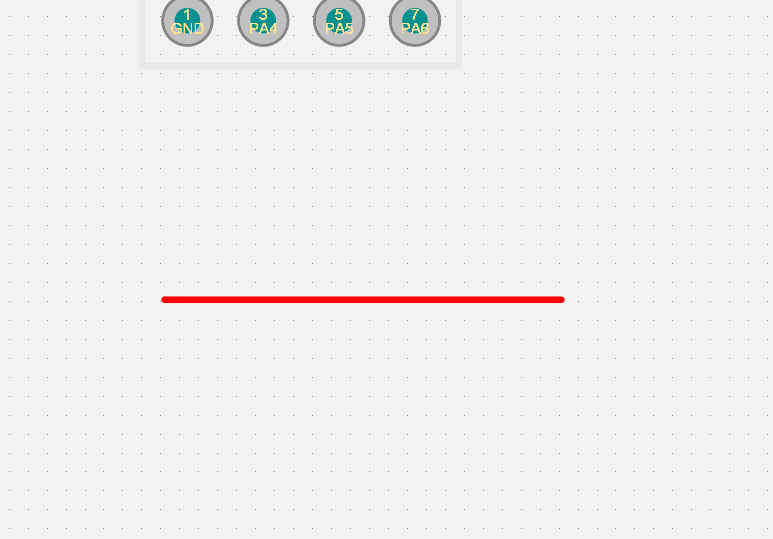

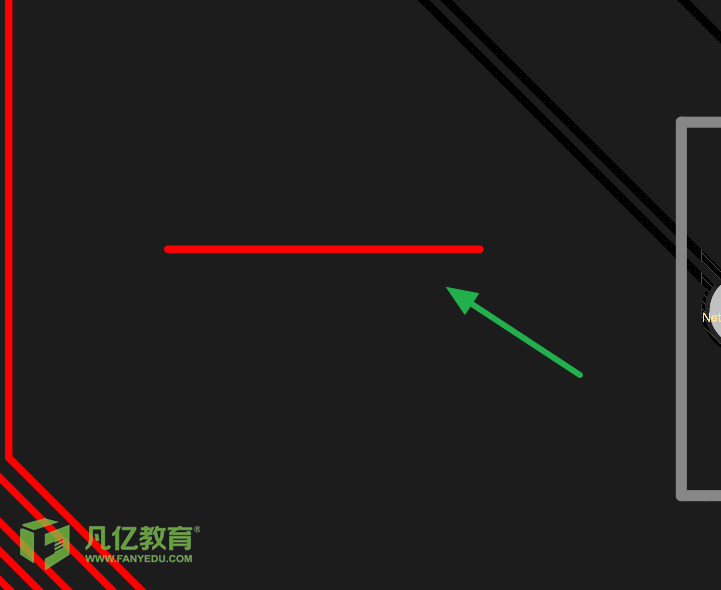

差分对内等长误差5mil2.锯齿状等长不能超过线距的两倍3.走线未连接到过孔中心,容易造成开路4.线宽尽量保持一致5.pcb上存在4出开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

在PCB设计的时候,总会碰到过载电流比较大的情况。我们知道过载电流的大小跟线宽的关系,过载电流如果大,对应的线宽我也要将它增宽。如果我们在某种情况下不能增宽走线的线宽,那么最常用的一种方法就是给走线镀锡。

PCB走线注意事项

USB走线控制90R,走线宽度6mil,中心间距12mil,这是我目前用的,这样是不是不符合3W了? 是不是要重新用SI9000计算一个符合90R同时符合3W的线宽和间距呢?

扫码关注

扫码关注