- 全部

- 默认排序

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

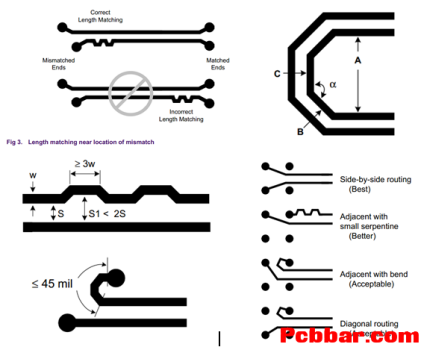

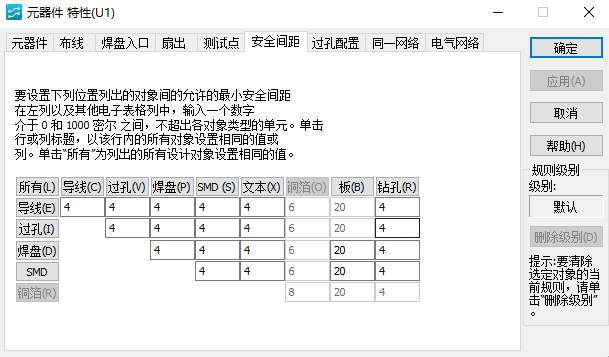

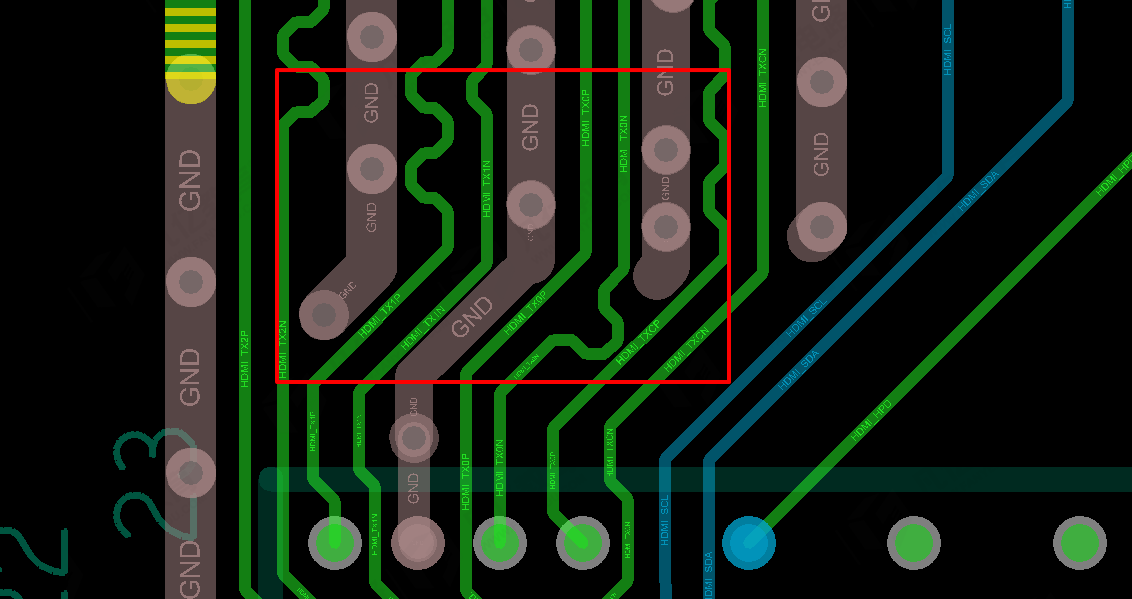

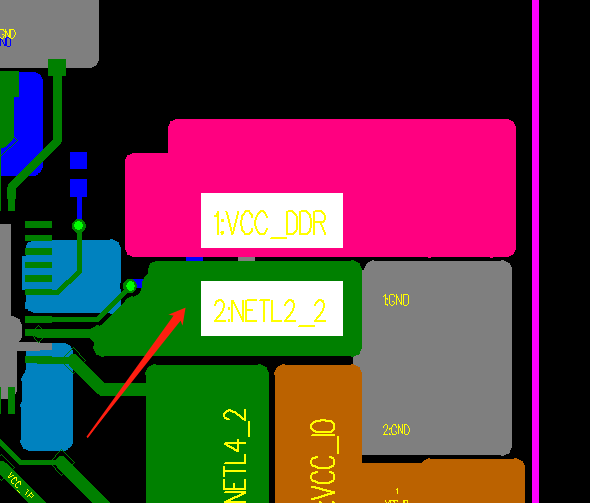

走线之间、走线到过孔间距太近,信号线之间尽量保持3w间距,信号线到地网络保持6-8mli差分走线保持间距,走线后注意修线差分对间线长超过误差,对间等长控制10mil误差以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特

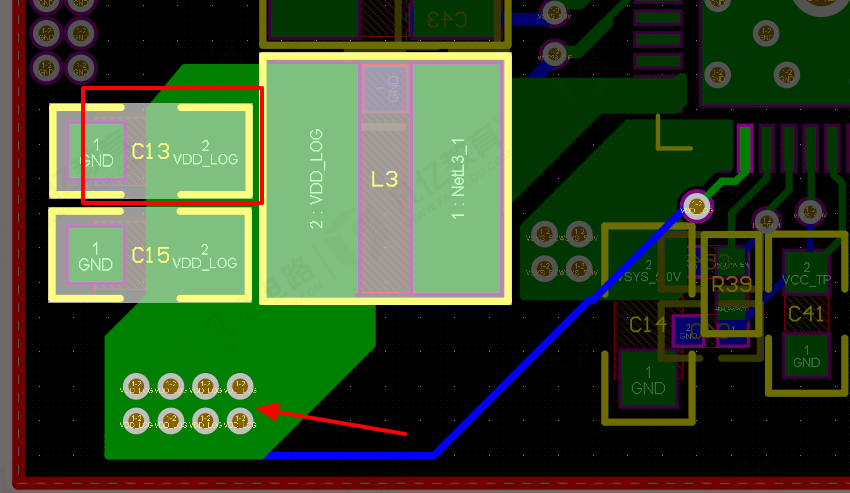

过孔打到最后一个器件后方,电容没有起到作用输入电源信号没有连通,底层应铺铜将输入电源连通多处飞线没有连通GND网络焊盘应就近打孔铜皮避让导致开路电源走线注意加粗走线在焊盘内应保持和焊盘一样宽,出焊盘后尽快加宽走线和焊盘不完全连接,尽量避免从

电感底部不要放置器件:可以吧电阻电容放置到中间IC的底部。电感内部也需要挖空处理:DCDC电源主干道建议铺铜处理满足其载流大小:LDO 电路部门扇孔注意过孔对齐:走线不要直角:LDO电源信号尽量拉出焊盘就加粗,不要拉出很多之后再去加粗:以

扫码关注

扫码关注