- 全部

- 默认排序

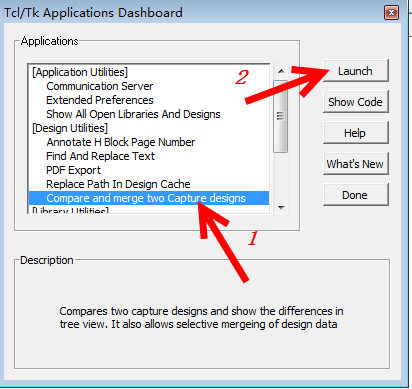

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

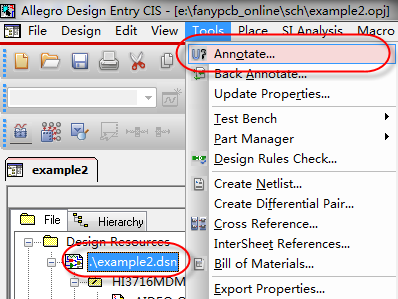

答:第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-52所示,进行原理图选项的编辑; 图3-52 原理图编译示意图第二步,在弹出的原理图编译界面中,如图3-53所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,如图3-54所示; 图3-53 原理图编译界面设置示意图 图3-54 原理图所有位号复

AD如何自动优化走线?

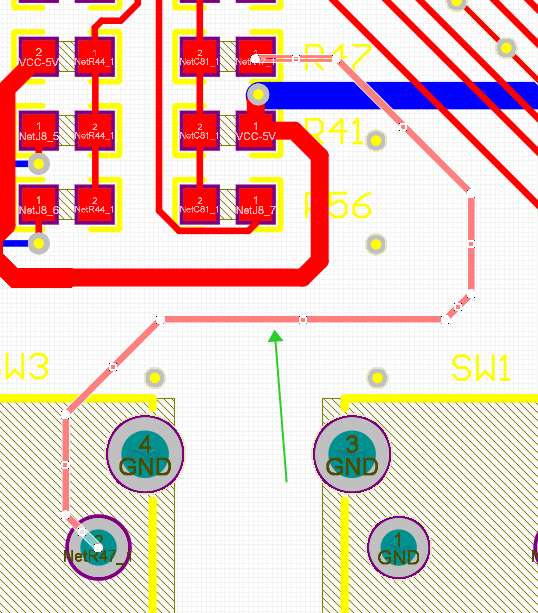

AD提供了一个“自动优化走线”的功能,可以在你走线需要优化的时候利用软件识别给布线做一个优化,选择所需要的优化,执行菜单命令【布线】-【优化选中走线】进行走线的优化,如图是优化前后对比,对路径进行了优化缩短,对于信号线越短,信号的完整性就会更好。

一般,批量添加封装到PCB板上有以下方法:第一步:点击菜单栏“ECO模式--添加元器件”如图,点击以后弹出如图界面。1)元件类型PCB封装必须得添加完元件类型,才能通过ECO模式添加到PCB界面里面,如若只是单个PCB封装的话,元件类型界面

这个方法一般用于从其它原理图里面保存需要的原理图封装文件,这样就省了自己去绘制的过程,会节省很多的时间。第一步:在原理图界面,执行菜单命令“设计--生成原理图库”。如图1所示。图1第二步:点击完成以后,会重新生成一个SCH Library。

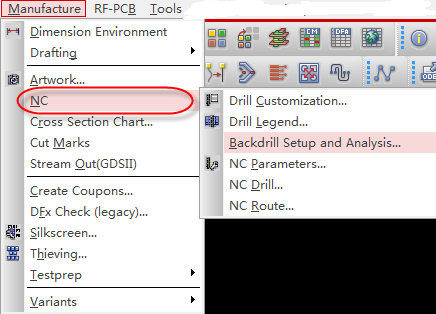

答:打开Allegro软件,点开Manufacture菜单栏,如图5-31所示,这是生产制造菜单栏下一些命令行。下面我们对Manufacture菜单栏下面的一些常用命令进行简单的介绍,具体知道是如何进行操作的,具体如下:

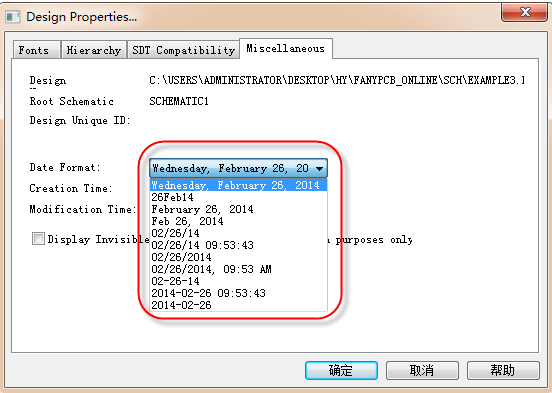

答:我们在使用Orcad软件进行原理图绘制的时候,新建原理图工程文件,默认在右下角都会出现Title Block,做为每个个原理图的一个显示内容,在左下角都有一个当前的时间显示,当前默认的这个Title Block的时间显示格式是,第一项是星期几,第二项是几月几日,第三项是年份,默认的格式都是这样的,我们对其进行修改的操作步骤如下所示:第一步,需要选中原理图根目录,执行菜单选项“Optiosn-Design Properties”,进行原理图设计属性的修改;第二步,进入设计属性之后呢,我们需要选

第一步:执行菜单命令“放置--多边形”如图1所示。图1第二步:双击放置的多变形,弹出属性编辑对话框。如图2所示,选择点击Fill Color后面的小方框既可修改它的填充颜色。图2

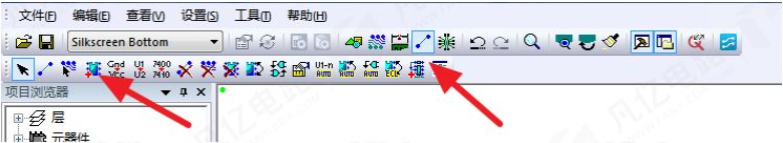

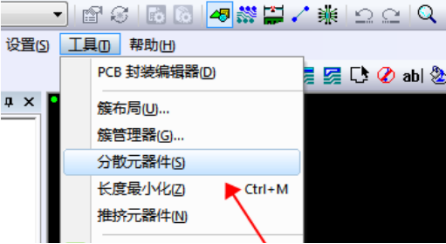

PADS分散元器件

布局时,有部分器件堆叠在一起,器件重叠导致选择不精准,而且一个一个抓开效率比较低,为了方便,可以使用分散元器件命令快速处理。1)若需要将整板的器件(除胶黏)进行打散,执行菜单栏“工具-分散元器件”。如图5-103、5-104所示。图5-10

扫码关注

扫码关注