- 全部

- 默认排序

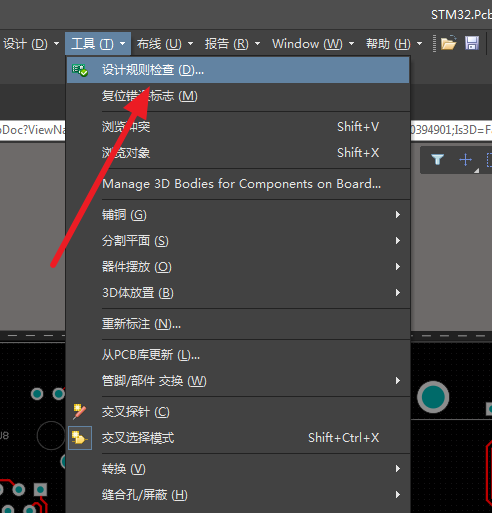

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。

干式绝缘结构是互感器诞生时的原型方式,其制造工艺简单、本钱较低,但因为其绝缘条件的约束,不能接受很高的电压,一般常用于380V及以下的场合。干式绝缘结构一般运用的绝缘资料有绝缘纸、玻璃丝布带和酚醛塑料等。二次绕组用QZ型漆包线,绕在酚醛纸筒

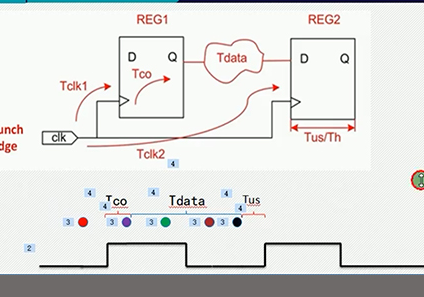

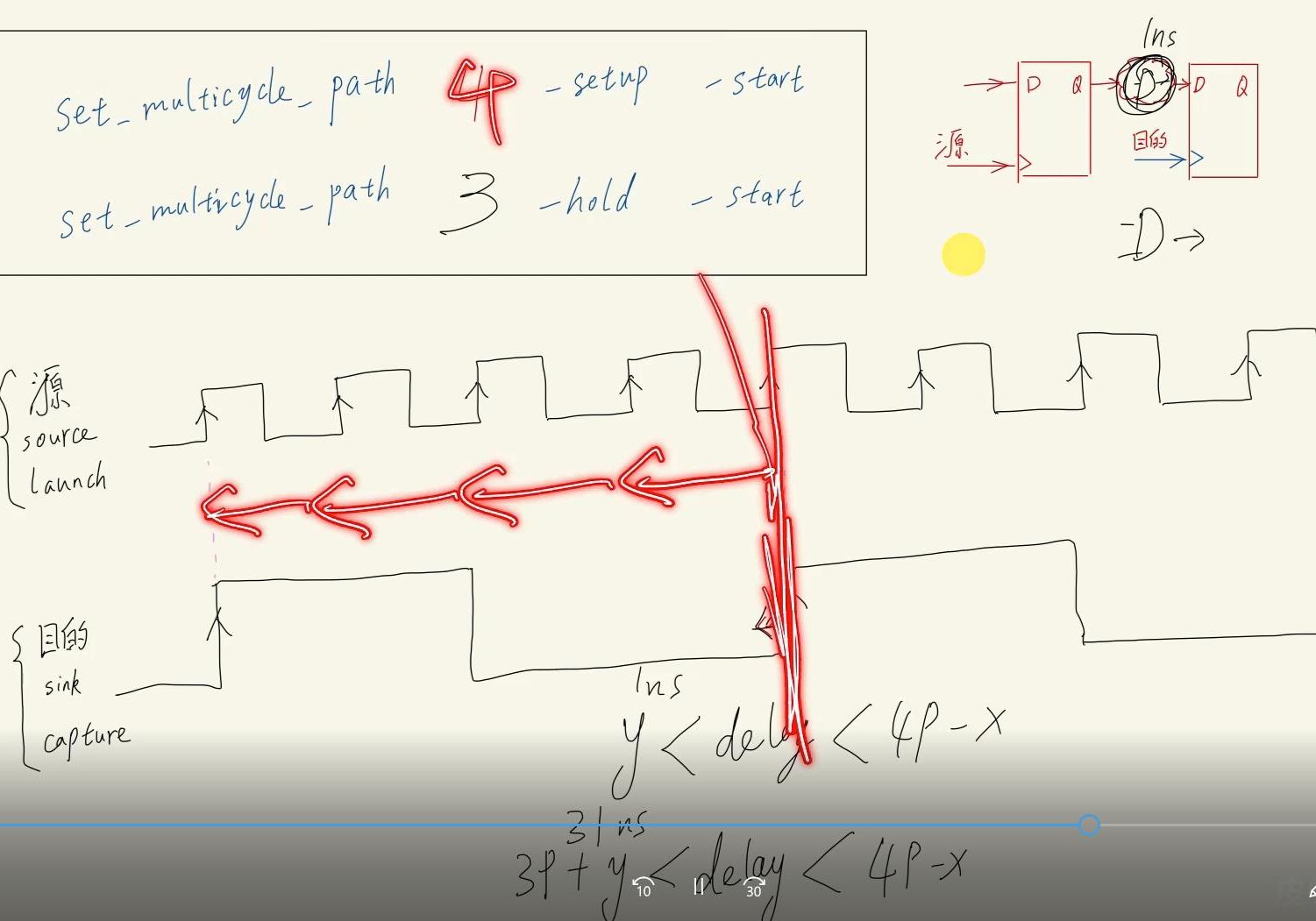

众所周知,芯片行业存在一个定理,那就是摩尔定律,主要内容是集成电路上可容纳的晶体管数目在大约每18个月便会增加一倍。掌握FPGA/IC工程师需要的核心技能,来凡亿教育!>>《基于VIVADO平台的FPGA时序约束教程》随着技术的提升和原材料

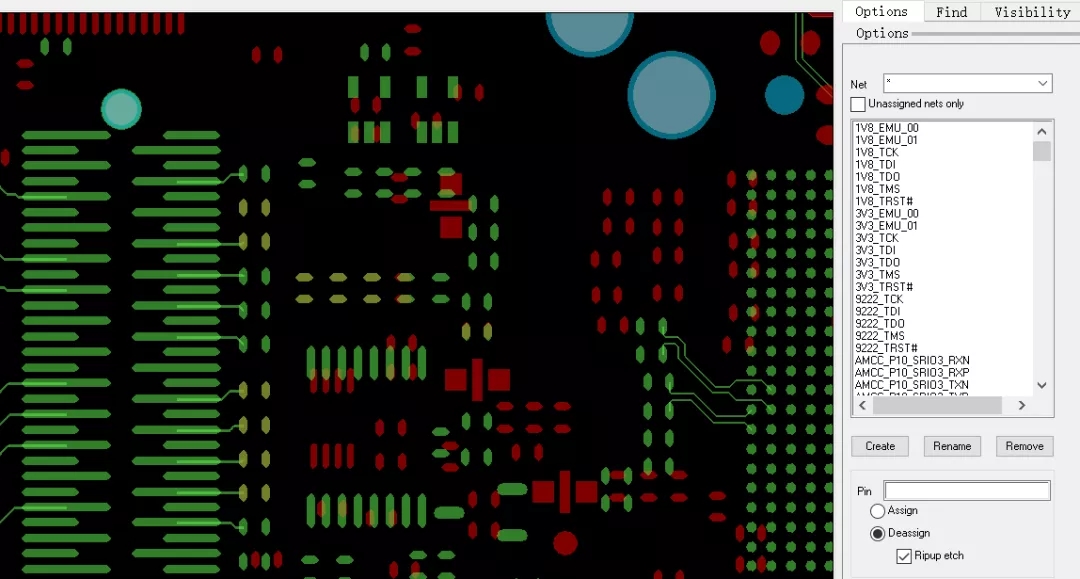

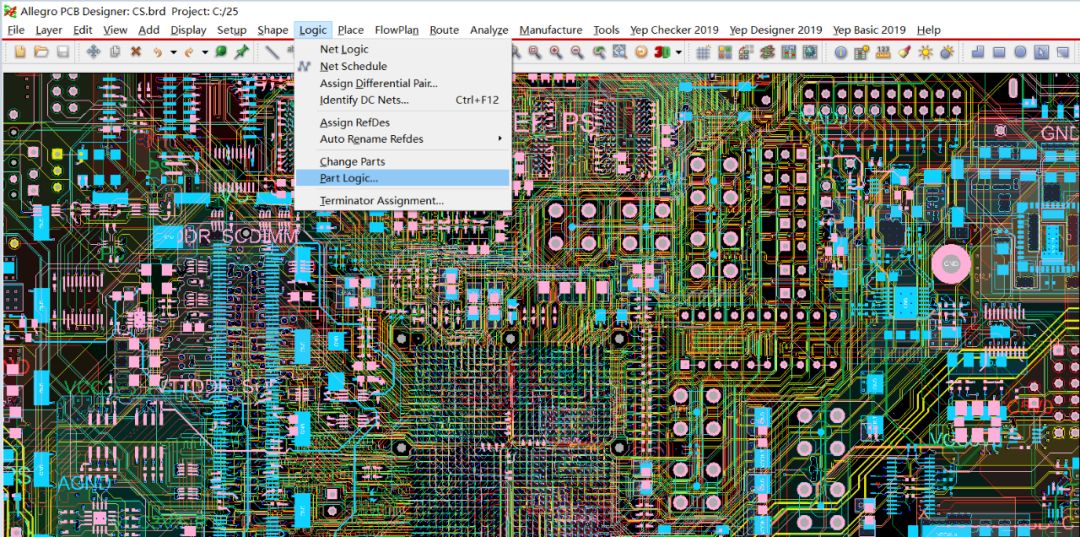

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

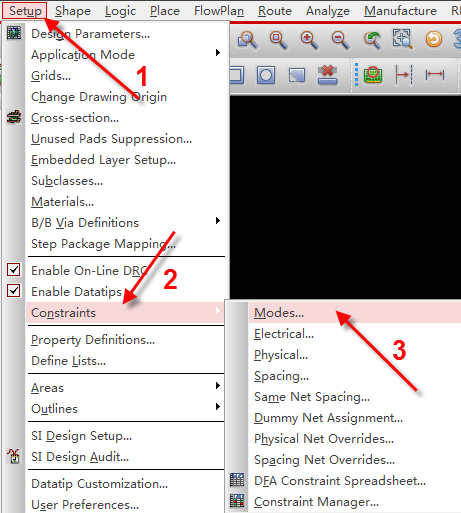

答:我们在前面的问答中讲述了走线的阻抗线宽以及不同的元素之间的间距规则之间的限定,但是,在Allegro软件中各个的约束规则需要在约束规则管理模式开启的情况下,才能起作用的。执行菜单命令Setup-Constrains,在下拉菜单中选择Modes,进行各个约束规则管理模式的选取,如图5-79所示:

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

本文介绍了如何通过使用ZPLM优化操作数在评价函数编辑器(Merit Function Editor )中使用ZPL宏定义复杂的优化目标。本文介绍了如何使用ZPLM约束系统的质心,以确保其能正确地平衡。作者 Alessandra Croce

RF和微波无源元件承受许多设计约束和性能指标的负担。根据应用的功率要求,对材料和设计性能的要求可以显着提高。例如,在高功率电信和军用雷达/干扰应用中,需要高性能水平以及极高功率水平。许多材料和技术无法承受这些应用所需的功率水平,因此必须使用专门的组件,材料和技术来满足这些极端的应用要求。高水平的射频

扫码关注

扫码关注