- 全部

- 默认排序

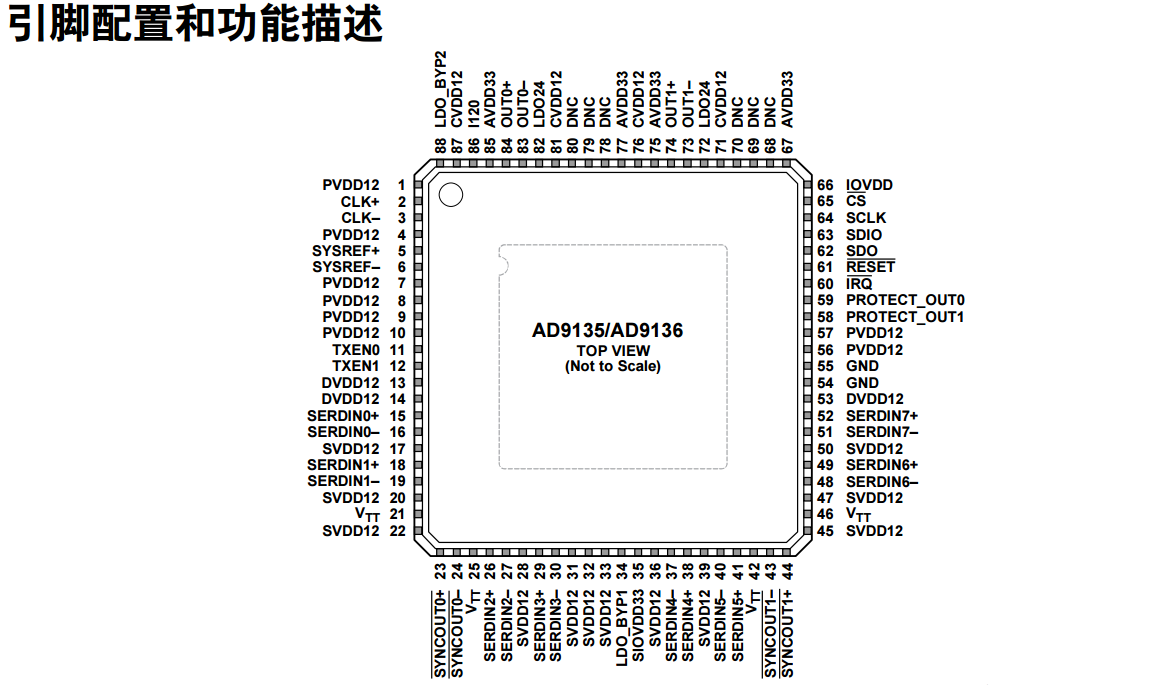

我们当遇到管脚数目比较复杂的元器件的时候,一个一个输入引脚功能和编号比较费时费力,也比较容易出错,cadence视频教你orcad怎么运用表格创建复杂的元器件?以后就可以熟能生巧啦,一起来看看吧!当我们在用orcad时,很多人都不知道怎么运用表格创建复杂的元器件,在这时可以借用excel表格来创建元器件,方便快捷。下面我们以AD9135/AD9136为例,详细分析借用excel表格来创建元器件的方法步骤,图4-1所示为AD9135/AD9136的封装信息资料。

我们进行PCB设计的时候,总会遇到再进行了敷铜操作,我们如何去更改对应网络的焊盘与铜皮之间的连接方式?我们首先可以来分析一下焊盘的连接方式有几种,分别为哪几种?运用AD进行PCB设计的人都清楚,焊盘的连接方式为三种:一个是全连接,一个是十字连接也就是我们经常所说的花焊盘连接,还有一个就是不连接意思就是不进行设置。

我们在进行PCB设计的时候,第一步就是进行元件库的创建,那么在进行元件设计的时候很多时候会碰到多管教的元件,如果我们一个一个去放置的话,就会非常的繁琐,浪费很多的时间。所以,我们今天就来讲解一下在AD中做元件库的的时候怎么快速放置很多管脚,而不是需要我们一个一个去点击放置。

在我们进行PCB设计的第一步就是进行元件库的创建,那么就会在元件库创建的时候碰负信号的存在。在元件库中负信号管脚名称的放置就会有很多学员不知道如何去进行设置了,我们今天要讲的内容就是AD管脚名称怎么进行负信号的放置。我们首先来看一下负信号大概是怎么标识的,看一下如下的截图:

NO ERC检查点就是忽略ERC检查点,是指这个点附加的元件的管脚在进行ERC的时候,如果出现错误或者警告将被忽略过去,不影响网络报表的生成。

在logic软件中绘制原理图,添加元器件后有些器件默认会显示器件的管脚名称、管脚编号、元件类型等信息,那怎样来进行隐藏,怎样对板上的器件进行批量属性显示与隐藏操作。

在我们进行高速pcb设计的时候,我们会遇到高度集成的BGA芯片,关于BGA的拉线打孔我们是如何去做的呢,对于一些简单的的BGA我们通常手工去拉线和打孔,但是对于一些管脚上千个的大BGA,显然手工拉线打孔是不现实的,其实我们Altium Designer软件集成了BGA自动扇出走线的功能,我们可以利用这个功能大大提高扇孔效率。现实设计当中很多学员无法扇出一个BGA的走线和打孔,是什么原因呢,我们借此视频也给大家讲述了相关的一些扇孔注意事项。

在LAYOUT中制作PCB封装时,在遇到焊盘管脚需要重新命名时,是有小技巧可以快速修改的。这个小视频介绍了封装焊盘管脚重新重名的小技巧。

扫码关注

扫码关注