- 全部

- 默认排序

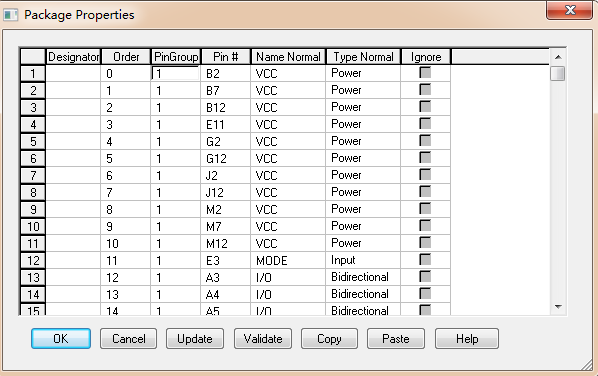

答:Pin Group这个属性是指可以交换的属性设置,我们删除这个属性的操作如下;第一步,打开库文件,点击菜单View→Package,进入到整个器件的编辑属性,然后点击菜单Edit→Properties,或者按快捷键Ctrl+E,进入器件管脚属性编辑页面,如图2-92所示: 图2-92 编辑器件属性示意图第二步,在弹出的器件属性框找到Pin Group这一栏,Pin Group这一栏中定义了数值,数值相同的就是可以进行管脚交换的,如图2-93所示; 图2-93&n

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC检查时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络表的生成。忽略ERC检查点本身不具有任何的电气特性,主要用于检查原理图

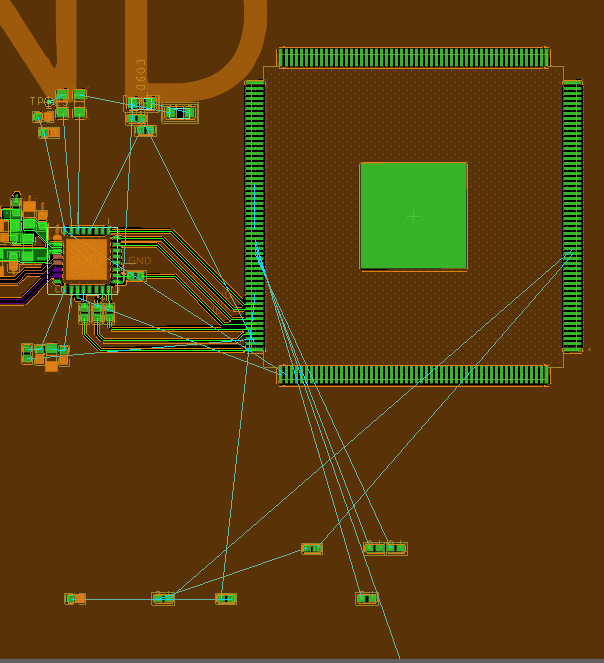

在进行PCB布线之前,都需要先做扇出工作,方便内层布线。对于电阻电容后者是小的IC类器件,可以直接进行手动扇出,但是对BGA类的器件,管脚数目太多,如图5-122所示,这样手工去扇出的话,工作量太大,而却BGA区间必须要扇孔在焊盘的中心位置,所以手动扇出是不现实的,这里我们讲解下,如何对BGA器件进行自动扇出,提高设计的效率,具体操作如下所示:

器件跟信号线还没有设计完全:器件之间注意间距,不要干涉了:注意器件需要整体对齐处理:此处器件重新放置下,注意整体对齐:器件就近IC管脚边放置:后期自己重新整体布局都优化下。差分打孔换层两边注意放置GND过孔:差分走线一定要耦合,此处完全不耦

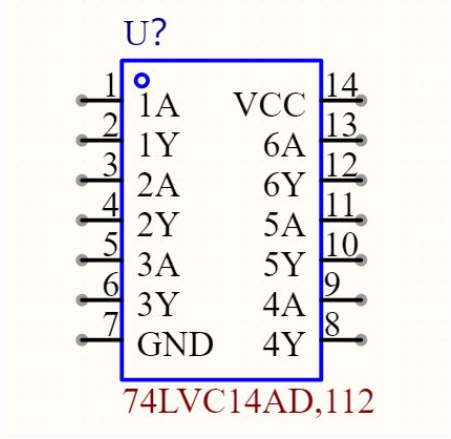

一、元件符号概述如图1所示,元件符号是元件在原理图中的表现形式,主要由元件边框、管脚(包括管脚符号和管脚名称)、元件名称及说明组成,通过放置的管脚来建立电气连接关系。元件符号中管脚序号是和电子元件实物的管脚一一对应的。在创建元件的时候,图形

答:在将网表导入到PCB的过程中,经常会出现封装内管脚名或者数目与原理图内的器件管脚不一致,从而导致导入过程中报错,如图4-90所示: 图4-90 导入网表提示解析示意图上图是一个比较典型的封装中管脚与原理图中不一致而出现的报错内容。从上示报错内容(红色框标识的内容)可以获取以下信息点:Ø 器件的封装名为ERF8-40。Ø 封装中有几个多余的管脚,管脚名为41、42、43、44、45、46、47、48。Ø 封装中缺少了几个管脚,管脚名为H1、H

扫码关注

扫码关注