- 全部

- 默认排序

出现这样的提示,如何解决呢?》allegro软件打开提示ERROR(SPMHDB-180):Design Revision 17.x is newer than Program Version

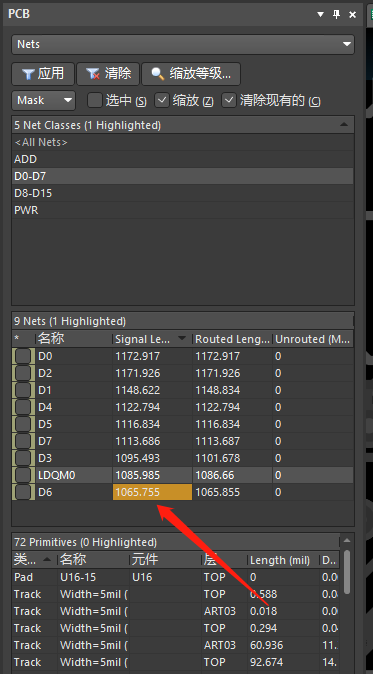

元器件能水平以及垂直方向放置,不要45度:不要有这种尖岬铜皮:机壳地与电路地至少满足2MM间距:差分对内等长注意参数长度值,gap需要大于等于3W:跨接器件两端都可多打地过孔:平面分割带建议加粗到20MIL:存在长度误差报错:以上评审报告来

数据线等长存在误差报错2.数据线与地址线之间的分割线上要打地过孔,建议150mil一个3.这几个信号也要加入地址线的类里面进行等长(就是片选,读写,行选,列选)4.注意器件摆放不要干涉5.地网络应该就近打孔,与第二层的地平面相连电源网络也同

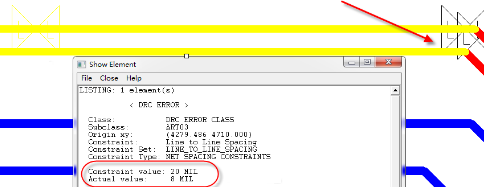

答:我们在PCB设计过程中,差分信号是比较重要的信号,一般设置差分信号到其它信号的间距是20mil,但是设置完差分信号到其它信号的间距之后,差分对内PN之间不满足20mil的间距,会报错,如图6-205所示:

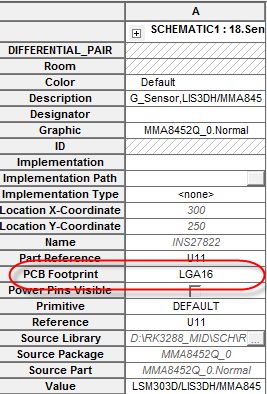

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36052): Value for property PCB Footprint contains carriage return for U11.解决的办法如下所示:第一步,错误的描述是这个器件的封装名称中含有回车键,所以在检查的时候不容易看出,需要将这个回车删除即可;第二步,找到报错的器件U11,双击这个器件,编辑器件属性,找到PCB Footprint这一栏,删除掉封装名名称后面的空格,如图3

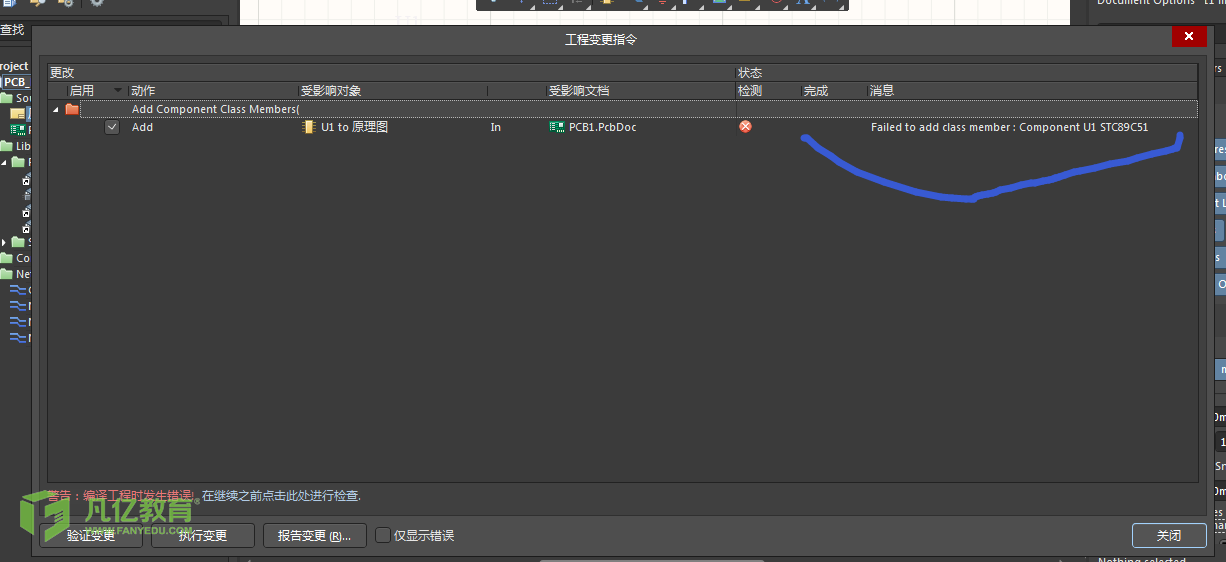

我们在进行到原理图导入到PCB中会出现各种各样的报错,之前的几种常见的报错我们也已经写过其对应的教程了,那么我们今天来看下出现“Failed to add class member”的这一项错误的解决办法。

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注