- 全部

- 默认排序

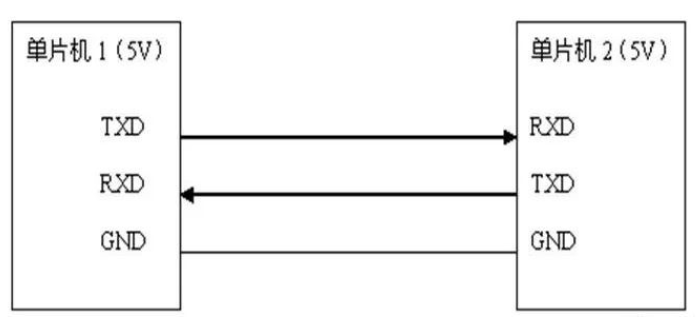

UART、I2C、RS485……这些通信虽然都普遍在用,但解释起来也是模棱两可,觉得有必要整理一下,目的是巩固和区分。文章有点长,建议先收藏,需要的时候再拿出来看。UART通用异步收发器UART口指的是一种物理接口形式(硬件)。UART是异

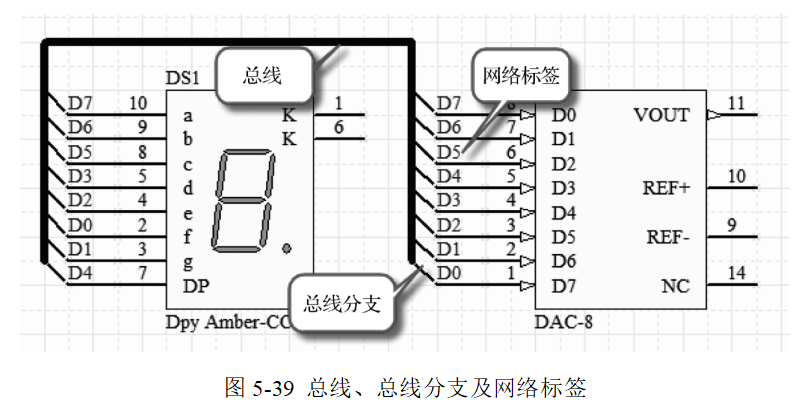

在我们PCB设计当中,为了提高直线效率我们走线不是一根一根的拉线的,因为这个样的速度是非常慢的,常见的经验工程师都是以总线的方式拉线,第一速度快,第二条理清晰,所以建议大家也用这种方式

开发板是用来进行嵌入式系统开发的电路板,包括中央处理器、存储器、输入设备、输出设备、数据通路/总线和外部资源接口等一系列硬件组件。说到开发板,就不得不提性价比之王MCU——ESP 32开发板。一.功能强大自带wifi 蓝牙是最大亮点!一起来看看ESP32的规格,就知道它强在哪里了。● 内置WiFi和

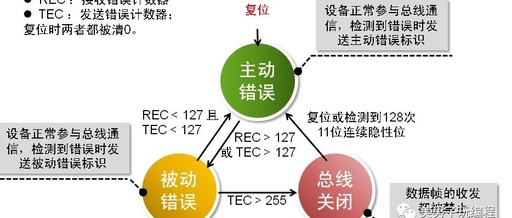

CAN通信是通过以下5种类型的帧进行的:数据帧 遥控帧 错误帧 过载帧 帧间隔另外,数据帧和遥控帧有标准格式和扩展格式两种格式。标准格式有 11 个位的标识符(Identifier: 以下简称 ID), 扩展格式有 29 个位的 ID。各种帧的用途如下表所示:近期打算写5篇文章,分别详细介绍这5种类

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

USB 2.0和USB 3.0是最常见的通用串行总线,也是应用广泛的输入输出技术规范,也是由Intel公司开发的总线架构之一,被广泛应用在个人电脑和移动设备等信息通讯产品,因此是工程师最为了解的接口之一,但很多人可能不太清楚USB 2.0/

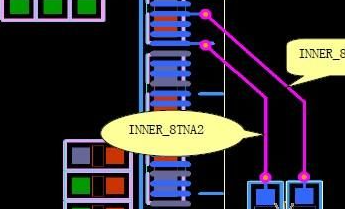

单纯的网络标签虽然可以表示图纸中相连的导线,但是由于连接位置的随意性,给工程人员分析图纸、查找相同的网络标签带来一定的困难。总线代表的是具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图。总线

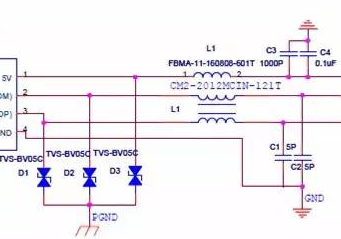

接口电路多种多样,一般需电缆引出的接口电路需要较完备的电磁兼容设计,如CAN总线、RS485总线;其他的接口电路如RS232、USB等一般采用磁珠加TVS管设计。1 RS485/CAN接口设计RS485接口标准电路如下:在具体设计中,R1

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

扫码关注

扫码关注