- 全部

- 默认排序

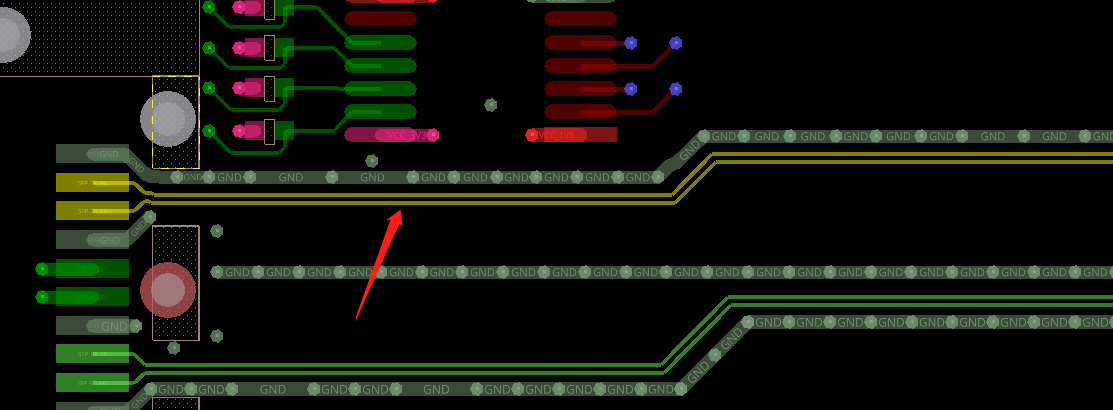

AD差分信号长度显示异常

大家好,一直搞不明白,设计差分信号和等长信号的线的时候,是需要在原理图就设置好,还是直接就在PCB设计的时候再设置呢?

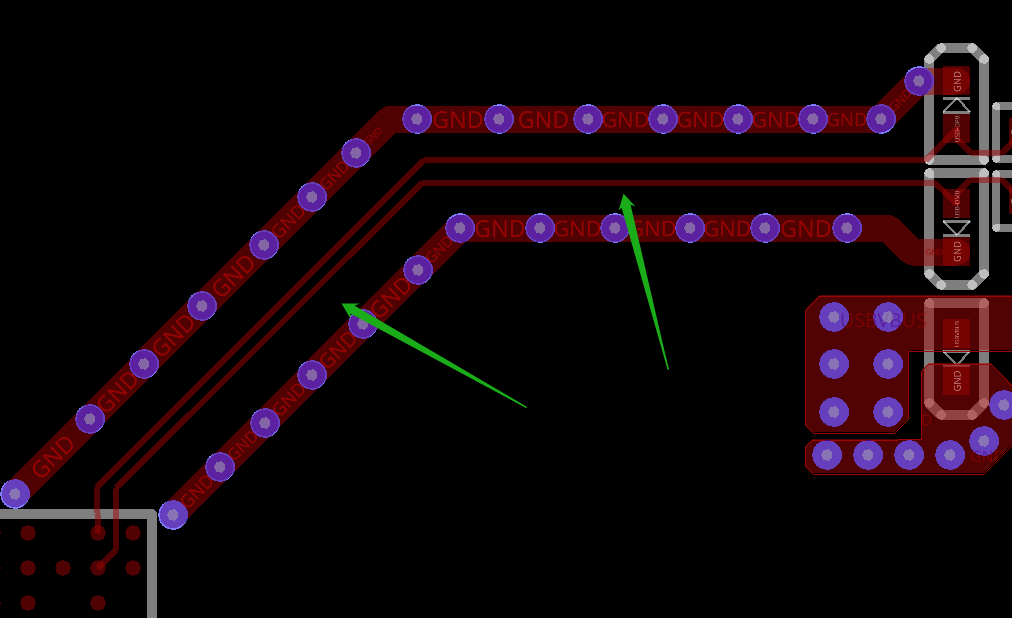

差分信号尽量包地包完全:此处上述一致原因,可以优化:此处电源信号的铜皮尽量优化宽一点,不然整体的铜皮载流量是从最窄处计算的:差分对内需要做等长处理,误差胃5MIL:此对差分没有做等长处理:其他的没什么问题。以上评审报告来源于凡亿教育90天高

USB2.0:差分走线是需要保持耦合,需要修改,不合格:USB3.0:还有一块铜皮存在板外,自己删除下:此处器件注意整体中心对齐放置:差分信号打孔换层的过孔两侧打上地过孔:此处差分需要优化,要耦合走线 :注意此处焊盘出线,需要从两侧边拉线出

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注